# PUNJAB TECHNICAL UNIVERSITY QUESTION PAPERS

### UNIVERSITY QUESTION PAPER, MAY-2019

#### SECTION - A

Q 1. (a) Multiply 1011.01 with 110.1.

Ans. Refer to Chapter No. 1 Q.No. 76

(b) Discuss the principle of duality.

Ans. Refer to Chapter No. 3 Q.No. 49

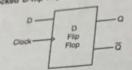

(c) Distinguish between combination and sequential logic circuits.

Ans. Refer to Chapter No. 5 Q.No. 15

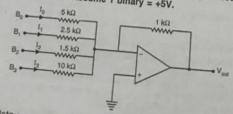

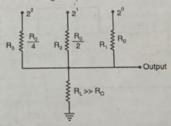

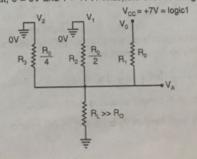

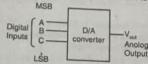

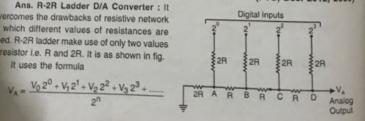

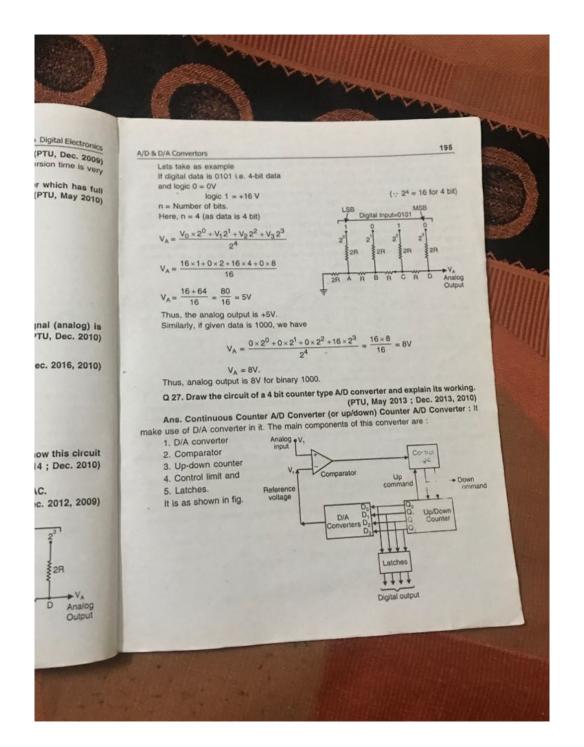

(d) Define R-2R ladder DAC.

Ans. Refer to Chapter No. 7 Q.No. 26

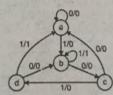

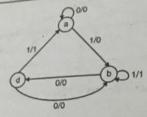

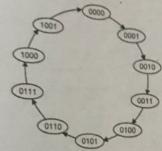

(e) What is the purpose of state diagram?

Ans. Refer to Chapter No. 5 Q.No. 82

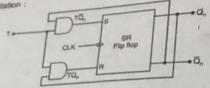

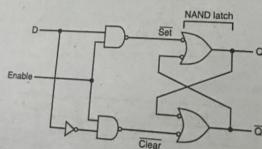

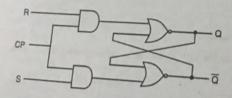

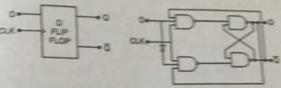

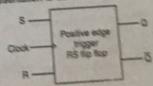

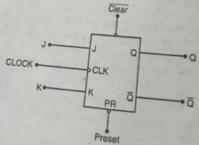

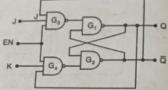

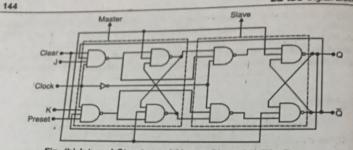

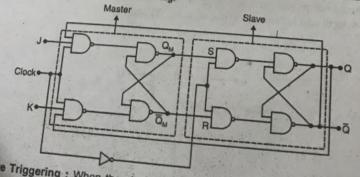

(f) Discuss race around condition in JK flip flop. .

Ans. Refer to Chapter No. 5 Q.No. 55

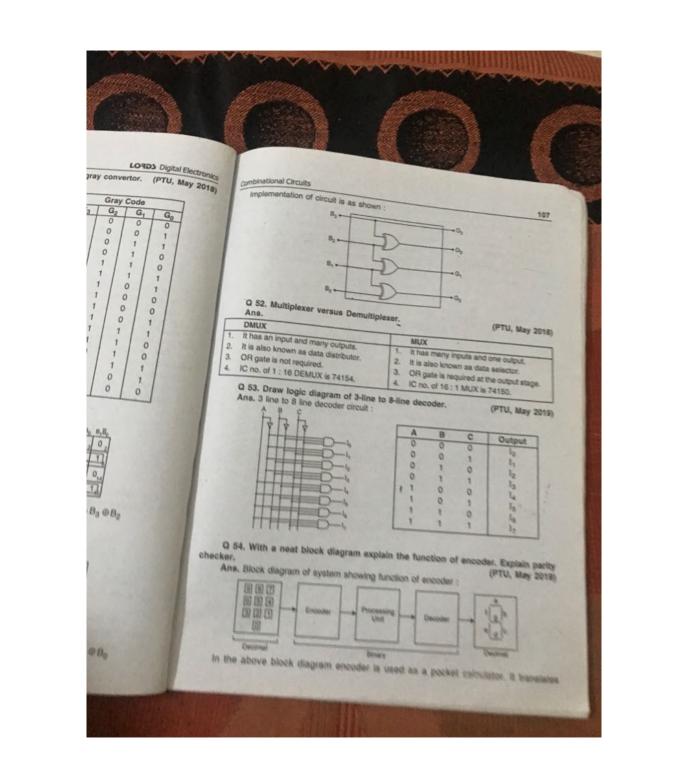

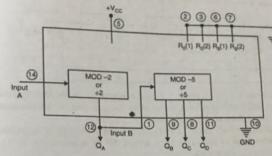

(g) Draw logic diagram of 3-line to 8-line decoder.

Ans. Refer to Chapter No. 4 Q.No. 53

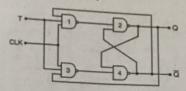

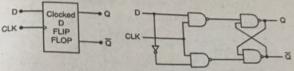

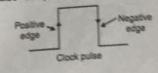

(h) Explain level triggering.

Ans. Refer to Chapter No. 5 Q.No. 67

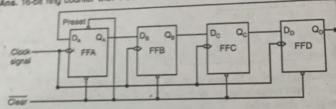

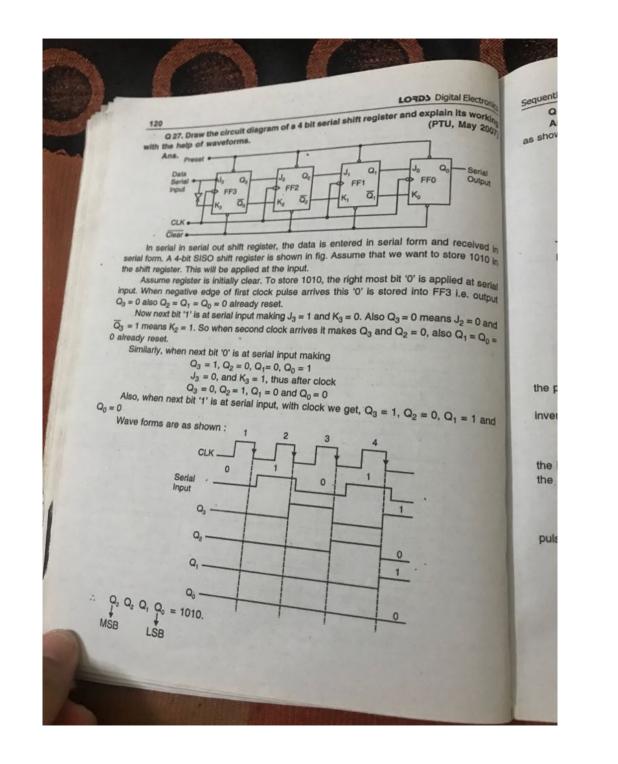

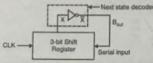

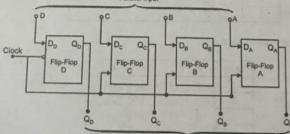

(i) What is serial-out shift register?

Ans. Refer to Chapter No. 5 Q.No. 38

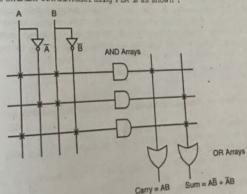

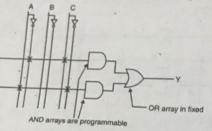

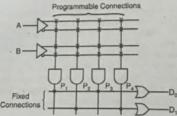

(j) Write short note on Programmable Logic Arrays.

Ans. Refer to Chapter No. 6 Q.No. 15

#### SECTION - B

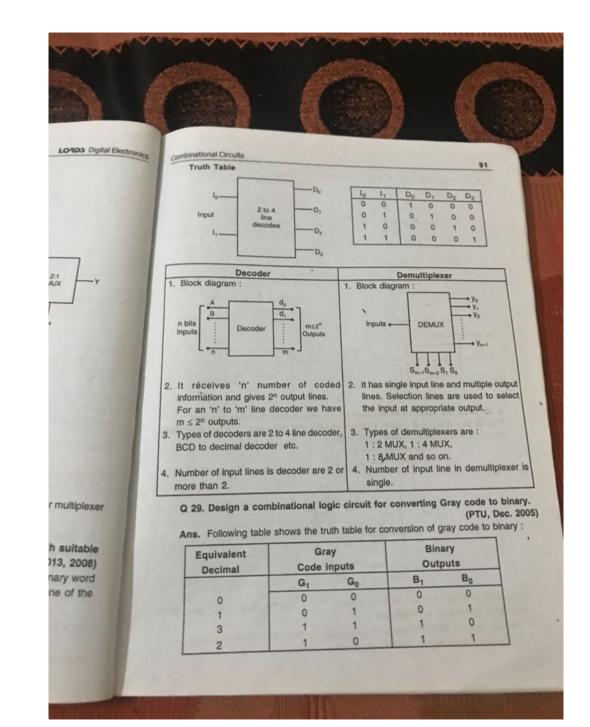

Q 2. What is the importance, applications and uses of Gray code?

Ans. Refer to Chapter No. 1 Q.No. 61

Q 3. Solve the following Boolean functions by using K-map.

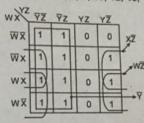

$F = (W, X, Y, Z) = \sum (0, 1, 4, 5, 6, 8, 9, 10, 12, 13, 14)$

Ans. Refer to Chapter No. 3 Q.No. 57

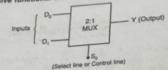

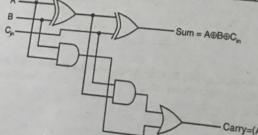

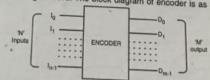

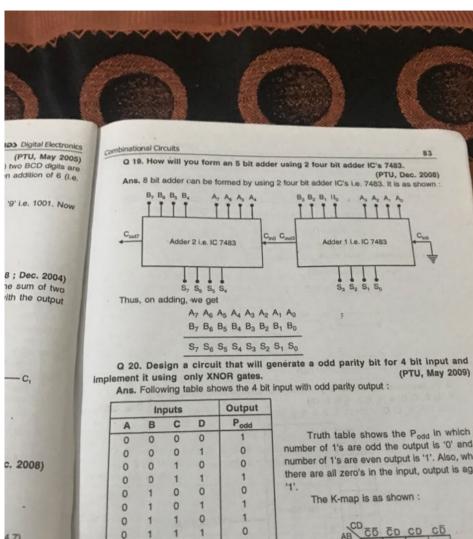

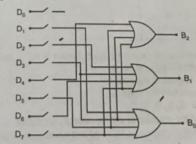

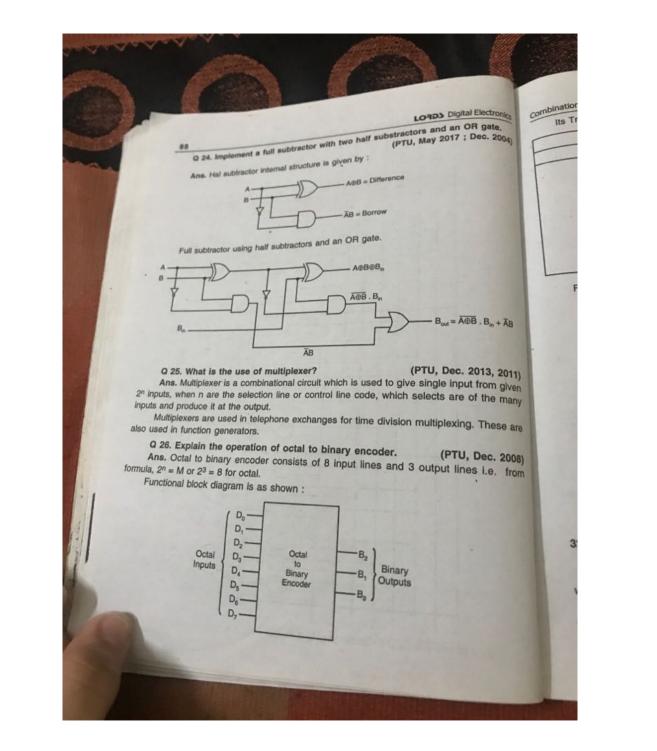

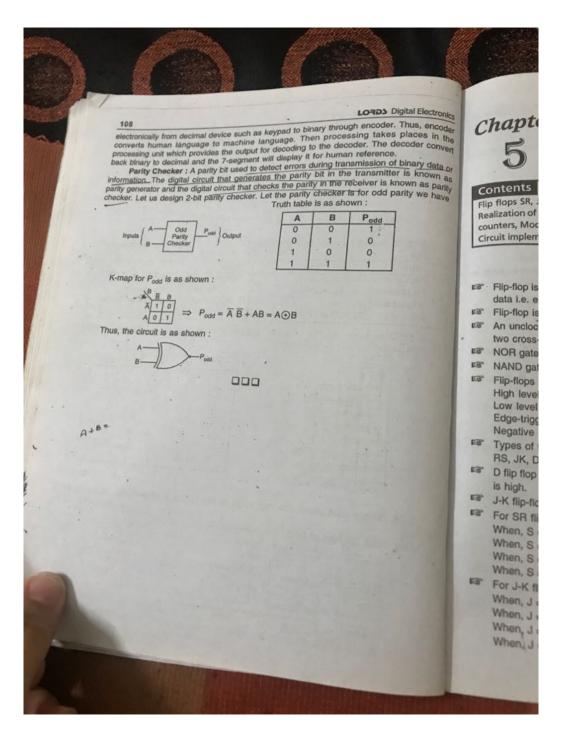

Q 4. With a neat block diagram explain the function of encoder. Explain parity

Ans. Refer to Chapter No. 4 Q.No. 54

Q 5. Discuss the advantages and disadvantages of TTL Logic Family.

Ans. Out of syllabus

LORDS Digital Electronics

rth complement =  $r^n - N$  for  $N \neq 0$ = 0 for N = 0

Alternately, it is defined as

rth's complement of a positive number N = its (rth's - 1) complement + 1

Le. (rth's - 1) complement

rth's complement (for positive number 'N')

- rar Numbers without +ve/-ve sign are unsigned numbers.

- sa Numbers represented by sign magnitude are signed numbers.

- BCD represent as 4 -bit binary code; also known as 8421 code.

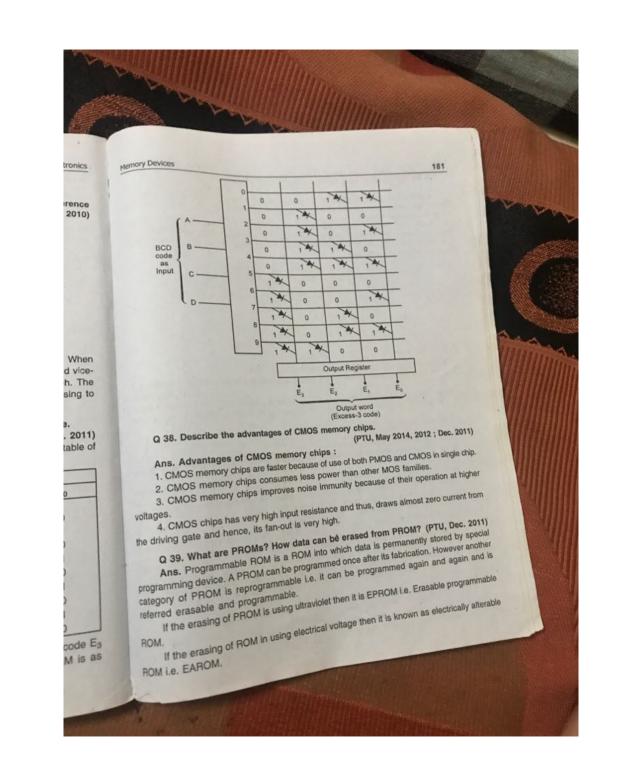

- EXCess-3 code is obtained by addition of three i.e. (0011)2 to BCD and is self complementary.

- Gray codes are reflected codes in which the successive coded characters differ in only 1

- Alphanumeric codes are represented by letters, symbols and numbers. These are ABCII codes, EBCDIC codes and ICII code.

### QUESTION-ANSWERS

Q 1. What is number system? What are its types? Give example for each type of

Ans. Number system: It is a set of rules and symbols, used to represent numbers. The number system can be classified into weighted or positinal and non-weighted or nonpositinal systems. Most of the number systems are of weighted type.

The knowledge of number system is very essential because the design and organisation of a computer is dependent upon the number systems. Few important points related to number

Base or Radix : It is defined as the number of different symbols used in the number system. The number of values that a character or digit can assume is called the Radix or

2. The largest value of a digit is always less than the Radix or Base: If Radix or Base is represented by 'r' or b', then the largest value of a digit is given by (r-1) or (b-1).

For e.g. The largest digit in decimal number system is (10 - 1) = 9. Where, 10 is the radix of decimal number system.

Types of Number System : Following table shows the various number system with their radix (r) or base (b).

| mons the      |

|---------------|

| Radix or Base |

| 2             |

| 8             |

| 10            |

| 16            |

|               |

Num

calle deci

digit

are a

binary

is:

and has

13

So 3, 1 octal nun

largest ve fr.

### Chapter

### **Number Systems**

Binary, Octal, Decimal, Hexadecimal. Number base conversions, 1's, 2's complements, signed Binary numbers. Binary Arithmetic, Binary codes: Weighted BCD, Gray code, Excess 3 code, ASCII.

### POINTS TO REMEMBER

- There are two input signals : analog signals have infinite number of distinct values and are contious, while digital signals have finite number of distinct values and are discrete

- Fair Types of number systems are : decimal, binary, octal, hexadecimal.

- Codes are representation of digital in specified format which include symbols, alphabets

- There are two logic levels in digital system : high (1) and low (0).

- There are two logic systems : positive and negative.

- Number system is a set of rules and symbols to represent numbers. It can be weighted

- Number of values that a character or digit can assume is called Radix or Base.

- Decimal number system has radix '10'. Leftmost digit is MSD and rightmost digit is LSD.

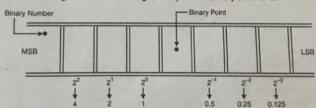

- Binary number system has radix '2' and two binary digits one '1' and '0'. Its weight is expressed as a power of 2.

- The smallest unit of information is called bit (0 and 1).

- Binary representation of four bits is called a Nibble.

- A byte is a combination of 8-binary bits.

- A word is a combination of 16-binary bits.

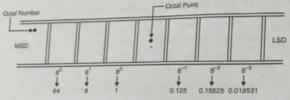

- Octal numbers system has radix '8' of the digits are (0 to 7). Its weight is expressed in

- Hexadecimal has radix '16'. The digits are 0 to 9 in continuation with letters A to F. Its weight is expressed in power of 16.

- 1's complement of a binary number is written by simply replacing all 0's by 1 and all 1's by 0.

- 2's complement is one increment of 1's complement.

- rth's complement : For a given positive number 'N' having radix 'r' or base 'r' with 'n' number of digits in integer part and 'm' number of digits in fractional part, the number 'N' for rth's complement in defined as

```

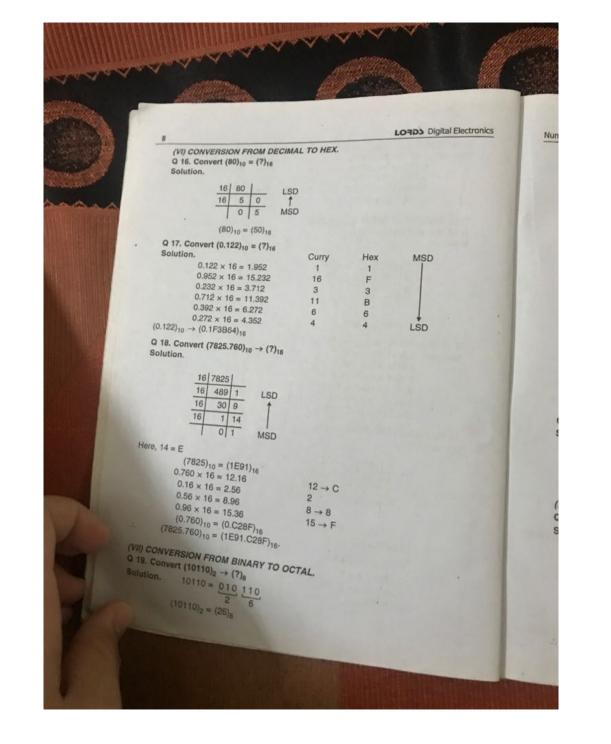

CONVERSION OF DIFFERENT NUMBERS

(I) CONVERSION FROM BINARY TO DECIMAL.

Q 1. Convert the binary number (110)2 to its decimal equivalent.

1x2 + 1x2 +0x2

Solution. (110)_2 = 1 \times 2^2 + 1 \times 2^1 + 0 \times 2^0

4+2+0

= 4 + 2 + 0 = 6

(110)_2 = (6)_{10}

Q 2. Convert the binary number (1011.01) to its decimal equivalent.

Solution. (1011.01)_2 = 1 \times 2^3 + 0 \times 2^2 + 1 \times 2^1 + 1 \times 2^0 \times 0 \times 2^{-1} + 1 \times 2^{-2}

= 8 + 0 + 2 + 1.0 + 0.25 = 11.25

(1011.01)_2 = (11.25)_{10}

Q 3. Convert the following :

Solution. (11011.111)_2 = 1 \times 2^4 + 1 \times 2^3 + 0 \times 2^2 + 1 \times 2^1 + 1 \times 2^0 + 1 \times 2^{-1}

+1×2-2+1×2-3

= 16 + 8 + 0 + 2 + 1 + 0.5 + 0.25 + 0.125

=(27.875)_{10}

(11011.111)_2 = (27.875)_{10}

```

(II) CONVERSION FROM OCTAL TO DECIMAL.

Q 4. Convert the following:

$$(71)_8 = (?)_{10}$$

Solution.  $(71)_8 = 7 \times 8^1 + 1 \times 8^0$

$= 56 + 1$

$= 57$

$(71)_8 = (57)_{10}$

Q 5. Convert the following:

Q 5. Convert the following:

$$(521.63)_8 = (?)_{10}$$

Solution.  $(521.63)_8 = 5 \times 8^2 + 2 \times 8^1 + 1 \times 8^0 + 6 \times 8^{-1} + 3 \times 8^{-2}$

$= 320 + 16 + 1 + 0.75 + 0.0468$

$= 337.7968$

$(521.63)_8 = (337.7968)_{10}$

Q 6. Convert the following:

Q 6. Convert the following:

$$(385.24)_8 = (?)_{10}$$

Solution.  $(385.24)_8 = 3 \times 8^2 + 8 \times 8^1 + 5 \times 8^0 + 2 \times 8^{-1} + 4 \times 8^{-2}$

$= 192 + 48 + 5 + 0.25 + 0.0625$

$= 245.3125$

$(385.24)_8 = (245.3125)_{10}$

It make use of first eight digits of decimal number system i.e. 0, 1, 2, 3, 4, 5, 6 and 7.

Thus, 8 and 9 digits never come in octal number system,

Octal positions values as a power of 8 are as shown:

e.g.

$$N = (431.32)_8$$

, find its decimal equivalent

=  $4 \times 8^2 + 3 \times 8^1 + 1 \times 8^0 + 3 \times 8^{-1} + 2 \times 8^{-2}$

$$= 4 \times 64 + 3 \times 8 + 1 \times 1 + \frac{3}{8} + \frac{2}{64}$$

$N = (281.40625)_{10}$

N = (431.32)<sub>8</sub> = (281.40625)<sub>10</sub>

4. Hexadecimal Number System : The number system having radix or base '16' is called as hexadecimal number system. In short these are known as hex system. The number of values assumed by each digit are 0 through 9 and letters A, B, C, D, E and F. Thus the

0, 1, 2, 3, 4, 5, 6, 7, 8, 9, A, B, C, D, E, F,

Here 'A' represents 10

'B' represents 11

'C' represents 12

'D' represents 13

'E' represents 14

'F' represents 15

The largest value or maximum value for the system is

$$(r-1) = (16-1) = 15$$

N =

$$(3FB)_{16}$$

, find its decimal equivalent

=  $3 \times 16^2 + F \times 16^1 + B \times 16^0$

=  $3 \times 256 + 15 \times 16 + 11 \times 1$

=  $76B + 250 + 11$

=  $(1019)_{10}$

N =  $(3FB)_{16} = (1019)_{10}$

Number Sys

(1) CC Q 1. Solut

> Q 2. Solut

Q 3. C

(1101 Soluti

(II) CO Q 4. C

$(71)_8 =$

Solution

Q 5. C

(521.63 Solutio

Q 6. Cc

(385,24

Solutio

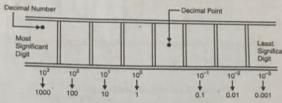

1. The Decimal Number System : The number system having radix or base '10' is called as decimal number system. The number which we make use in our life is called the decimal number system.

The decimal system has the base value of 10. So, its maximum or largest value of a digit is (r-1) = 10 - 1 = 9, where r = radix or base. Decimal position values as powers of 10 are as shown:

e.g.

$$N = (786.182)_{10}$$

$(786.182)_{10} = 7 \times 10^2 + 8 \times 10^1 + 6 \times 10^0 + 1 \times 10^{-1} + 8 \times 10^{-2} + 2 \times 10^{-2}$

2. Binary Number System: The number system having radix or base '2' is called as binary number system.

As the radix or base value of binary number system is '2', so its maximum value of digit is:

$$(r-1)=(2-1)=1$$

, where r is radix or base.

The two binary digits are '1' and '0'. In binary system each binary digit is known as bit and has its own weight or value. Its weight is expressed as a power of 2.

e.g. N = (1100.011)2, find its decimal equivalent.

$$1 \times 2^{3} + 1 \times 2^{2} + 0 \times 2^{1} + 0 \times 2^{0} + 0 \times 2^{-1} + 1 \times 2^{-2} + 1 \times 2^{-3}$$

$N = (12.375)_{10}$

$$N = (1100.011)_2 = (12.375)_{10}$$

3. Octal Number System: The number system which make use of radix '8' is known as octal number system. As the radix or base of octal number system is '8', so its maximum or largest value of a digit is

$$(r-1)=(8-1)=7$$

where r is radix or base.

is self

only 1

ABCII

/pe of

nbers. r\_non-

> sation ımber

mber dix or

dix or - 1). s the

with

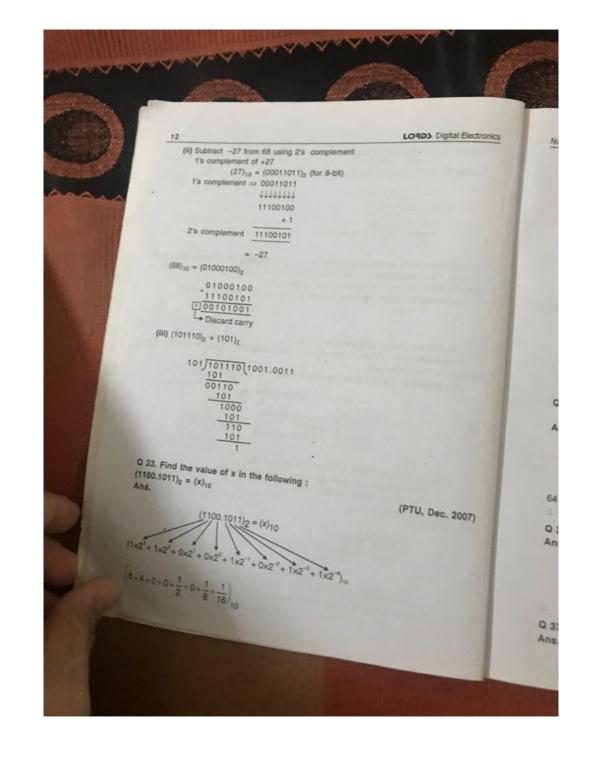

and Electronics Number Systems Case I: 1's complement of smaller number is :  $(11001)_2 \rightarrow (00110)_2$ 11 Case II: Add 1's complement to larger number: 11101 +00110 100011 around 00100 Final result Q 31. Define 1's and 2's complements. Ans. 1's complement : When the given binary number is inverted once i.e. complemented once than it is known as 1's complement. For example : Let the binary number be (1101)2 so, its 1's complement is : ++++ 0010 Whole of the data is complemented once. 2's complement : When 1 is added to the 1's complement of the binary number then it is known as 2's complement. For example : For the binary number (1101)2. 0 0 1 0 -> 1's complement + 1 → Add 1 0 0 1 1 → 2's complement Q 32. (i) Convert 2222 in Hexadecimal number. (ii) Subtract -27 from 68 using 2's complements. (iii) Divide (101110)<sub>2</sub> by (101)<sub>2</sub>. (PTU, May 2008) Ans. (i) (2222)<sub>10</sub> = (?)<sub>16</sub> 2009) 16 | 2222 16 | 138 14  $(2222)_{10} = (8AE)_{16}$ (: 10 = A and 14 = E in Hexadecimal) 009)

10

(X) CONVERSION FROM HEXADECIMAL TO OCTAL. Q 26. Convert (1AF)16 -> (?)8 Solution.

$$\frac{000}{0} \, \frac{110}{6} \, \frac{101}{5} \, \frac{111}{7} = 657$$

$(1AF)_{16} = (657)_8$

Q 27. Convert (3CFB.2E)<sub>16</sub> = (?)<sub>8</sub> Solution.

3 C F B 2 E (0011 1100 1111 1011 0010 1110),

$$\underbrace{000}_{0}\,\underbrace{011}_{3}\,\underbrace{110}_{6}\,\underbrace{011}_{3}\,\underbrace{111}_{7}\,\underbrace{011}_{3}\,\cdot\,\underbrace{001}_{1}\,\underbrace{011}_{3}\,\underbrace{100}_{4}$$

(3CFB.2E)<sub>16</sub> = (36373.134)<sub>8</sub>

Q 28. Convert (68.4B)<sub>16</sub> = (?)<sub>8</sub> Solution.

0110 1000-0100 1011

$$\underbrace{\frac{001}{1}}_{1} \underbrace{\frac{101}{5}}_{0} \underbrace{\frac{000}{0}}_{0} \cdot \underbrace{\frac{010}{2}}_{2} \underbrace{\frac{010}{6}}_{10}$$

$(64.4B)_{16} = (150.226)_8$

Q 29. Solve (11001)<sub>2</sub> - (10101)<sub>2</sub>.

Ans. 11001 - 10101 00100

(PTU, May 2009)

$(11001)_2 - (10101)_2 = (00100)_2$

Q 30. Subtract (11001)<sub>2</sub> from (11101)<sub>2</sub> using 1's complement method.

Ans. (11101)2 - (11001)2 using 1's complement method is given by : (PTU, May 2009)

is k

Q 20. Convert  $(11010010)_2 \rightarrow (?)_8$ Solution.  $11010010 = \underbrace{011}_{3} \underbrace{010}_{2} \underbrace{010}_{2}$

$(11010010) = (322)_8$

$(0.1011011)_2 \rightarrow (0.554)_8$

(VIII) CONVERSION FROM BINARY TO HEXADECIMAL.

Q 22. Convert (1010111)<sub>2</sub> → (?)<sub>16</sub>

Solution. 1010111 = 01010111

$(1010111)_2 = (57)_{16}$

Q 23. Convert (1010 1111 1011 0010)<sub>2</sub>  $\rightarrow$  (?)<sub>16</sub> Solution.

(1010 1111 1011 0010)<sub>2</sub> = (AFB2)<sub>16</sub>

Q 24. Convert  $(10110110.101111001)_2 \rightarrow (?)_{16}$  Solution.

$(10110110.1011111001)_2 = (B6.BC8)_{16}$

(IX) CONVERSION FROM OCTAL TO HEXADECIMAL. Q 25. Convert  $(436)_8 \rightarrow (?)_{16}$  Solution.

4 3 6 ↓ ↓ ↓ 100 011 110

$(436)_8 = (100011110)_2$

000100011110 1 1 D

$(436)_8 = (11D)_{16}$

13

$(12.6875)_{10}$  $(X)_{10} = (12.6875)_{10}$

Q 34. Convert the following binary numbers to decimal

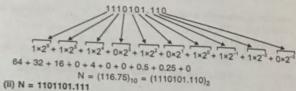

(i) 1110101.110 (ii) 1101101.111 Ans. (i) N = 1110101.110

(PTU, Dec. 2013)

4 + 32 + 0 + 8 + 4 + 0 + 0 + 0.5 + 0.25 + 0.125 $N = (108.875)_{10} = (1101101.111)_2$

Q 35. Convert the following binary number in decimal 1110101.

(PTU, May 2007)

Ans.  $(1110101)_2 = (?)_{10}$

$$64 + 32 + 16 + 0 + 4 + 0 + 1 \Rightarrow (117)_{10}$$

$\therefore (1110101)_2 = (117)_{10}.$

Q 36. Convert (10101)<sub>2</sub> to decimal number system. (PTU, May 2018 ; Dec. 2006) Ans.  $(10101)_2 = (?)_{10}$

$$1 \times 2^{4} + 0 \times 2^{3} + 1 \times 2^{2} + 0 \times 2^{1} + 2^{0} \times 1 \Rightarrow 16 + 0 + 4 + 0 + 1 = 21$$

$$(10101)_{2} = (21)_{10}$$

Q 37. Convert hexadecimal number F3A7C2 to binary.

(PTU, Dec. 2006)

Ans.  $(F3A7C2)_{16} = (?)_2$

2007)

Andrewander

Q 46. What is a BCD code? What are its advantages and disadvantages? (PTU, Dec. 2009; May 2015, 2009)

Ans. BCD Code: BCD is the binary coded decimal code for the representation of

digital data. It is a 4-bit binary number for each decimal digit. For example : If 72 is the decimal number then its BCD code is given as :

Advantages of BCD code :

- 1. It make use of only 0 to 9 decimal number, thus the binary equivalent of 0 to 9 is

- 2. It is similar to the decimal number system but has 4-bit binary equivalent.

- Disadvantages of BCD code : 1. BCD code needs more number of binary bits then simple binary number for representation in decimal.

For example :  $(2)_{10} = (10)_2 = (0010)_{BCD}$ .

2. Addition and subtraction of BCD make use of different rules.

Q 47. Convert decimal 177.25 to octal number.

(PTU, May 2017; Dec. 2008)

Ans. (a) (177.25)<sub>10</sub> = (?)<sub>8</sub> Integer Part

Fractional Part

$$0.25 \times 8 = 2.00$$

$(0.25)_{10} = (0.2)_{8}$

Q 48. Perform following subtraction (i) 11001 - 10110 using 1's complement.

(ii) 11011 - 11001 using 2's complement. Ans. (i) 11001 - 10110

Using t's complement, the steps are :

1. Calculate the 1's complement of smaller number

01001 ← 1's complement

(PTU, Dec. 2008)

```

tronics

Number Systems

Q 41. Write the first four decimal digits in base 4.

Ans. The first four decimal digits in base 4 are :

(PTU, Dec. 2005)

0, 1, 2 and 3.

cimañ:

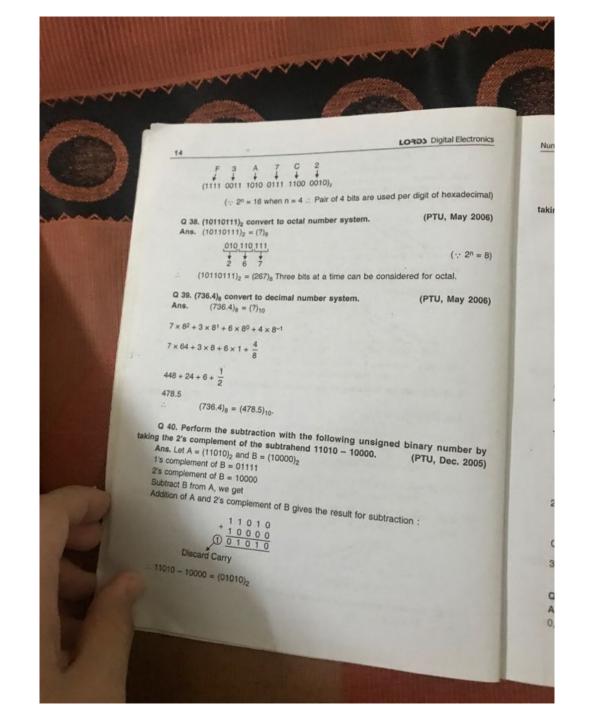

Q 42. Perform the subtraction with the following unsigned binary number by

taking the 2's complement of the subtrahend. 1101 - 1000.

2006)

(PTU, May 2005)

Ans. (11010)<sub>2</sub> - (1000)<sub>2</sub>

Smaller number is (01000)<sub>2</sub>

its 1's complement is (10100)2

and 2's complement is (10101)2

= 8)

Add 2's complement of smaller number in larger number, we get :

11010

+10101

(9005)

101111

Discard Carry

Thus, (01111)2 is the final result.

Q 43. Write the first four decimal digits is base 6.

(PTU, May 2005)

Ans. 0, 1, 2, 3 are the first four decimal digital in base 6.

Q 44. Solve (10101)2 - (10011)2.

(PTU, Dec. 2009)

Ans. (10101)<sub>2</sub> - (10011)<sub>2</sub>

(10101)<sub>2</sub> = (21)<sub>10</sub> ← Larger number

(10011)<sub>2</sub> = (19)<sub>10</sub> ← Smaller number

1. Calculate 2's complement of smaller number, we have

10011 ← Smaller number

by

01100 ← 1's complement

05)

+1

01101 ← 2's complement

2. Add the 2's complement to larger number, we have

10101 ← larger number

+01101

Carry ← 100010

3. If carry comes discard the carry, we get

(00010)2 which is the final result.

Q 45. Write the first four decimal digits in base 7.

(PTU, Dec. 2004)

Ans. The first four decimal digits in base 7 are :

0, 1, 2, 3.

```

|     | K & W | 200 |     |       |

|-----|-------|-----|-----|-------|

| Num | ber   | Sy  | ste | ms    |

| -   | _     |     | 200 | 77.79 |

Gray Code: Gray code is mainly used in shaft position encoders. A shaft position encoder basically produces a code word which represents the angular position of the shaft. Excess-3 code: It is non-weighted code. It is derived from 8421 BCD code. It is a sequential and self complimenting code.

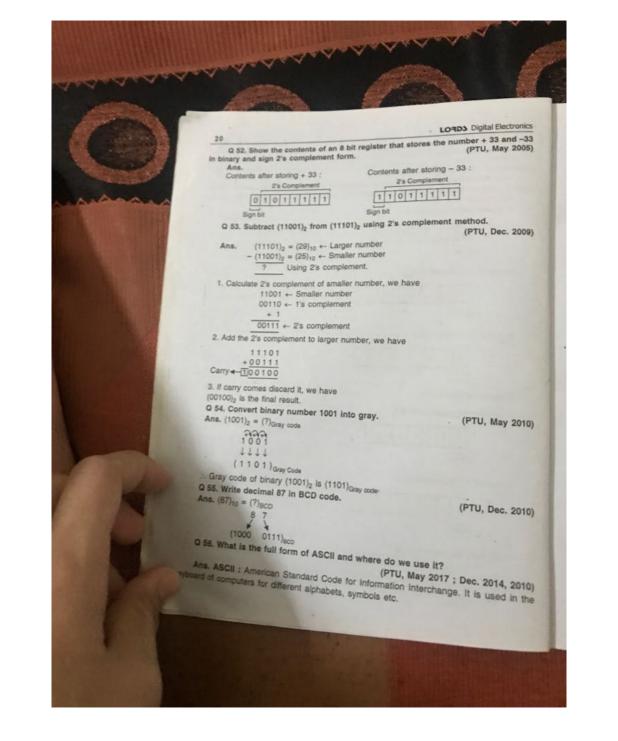

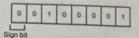

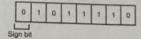

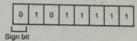

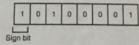

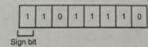

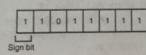

Q 51. Show that the contents of an 8 bit register that stores the number +33 in sign 1's complements and sign 2's complement form. Ans. Number N = +33 (PTU, Dec. 2005)

Its signed magnitude form is:

Its signed 1's complement is :

Its signed 2's complement is :

Similarly, when N = -33

Its signed magnitude form is:

Its signed 1's complement is :

Its signed 2's complement is:

Dec. 2017) e. In binary only these Numbers (d)  $(12.354)_{10} = (x)_2$

| 2 | 12  | 1 | -10  |

|---|-----|---|------|

| 2 | 6   | 0 | - LS |

| 2 | 3   | 0 |      |

| 7 | 1   | 1 | Ť    |

| M | ISB | - | _    |

$$\therefore (12)_{10} = (1100)_2$$

Similarly

$$0.354 \times 2 = 0.708$$

0  $0.708 \times 2 = 1.416$  1  $0.416 \times 2 = 0.832$  0  $0.832 \times 2 = 1.664$  1  $0.664 \times 2 = 1.328$  1  $0.328 \times 2 = 0.656$  0  $0.656 \times 2 = 0.312$  0

(e)

$$(BEE)_x = (2699)_{10}$$

$$11 \times x^2 + 14 \times x + 14 = 2699$$

$$11x^2 + 14x = 2685 \Rightarrow 11x^2 + 14x - 2685 = 0$$

$$x = \frac{-14 \pm \sqrt{(14)^2 - 4 \times 11 \times (-2685)}}{2 \times 11}$$

$$=\frac{-14\pm\sqrt{196+118140}}{22}$$

$$x = \frac{-14 \pm \sqrt{118336}}{22}$$

$$x = \frac{-14 \pm 344}{22}$$

either,

$$x = \frac{330}{22}$$

or  $x = \frac{-358}{22}$

$$x = 15$$

or  $x = -ve$  value and is not possible  $x = 15$ .

Q 50. What are ASCII codes ? What are their applications ? Ans. ASCII: American standard code for Information interchange is a 7 bit code. In binary ans. ASUL: American standard code for information intertriaingle is a 7 bit code in original signals, only two symbols 0 and 1 are used. It is not enough to communicate using only these two symbols between two computers. Users require 26 alphabets capital and small. Numbers 9, punctuation marks and many other symbols. This all is available in ASCII code.

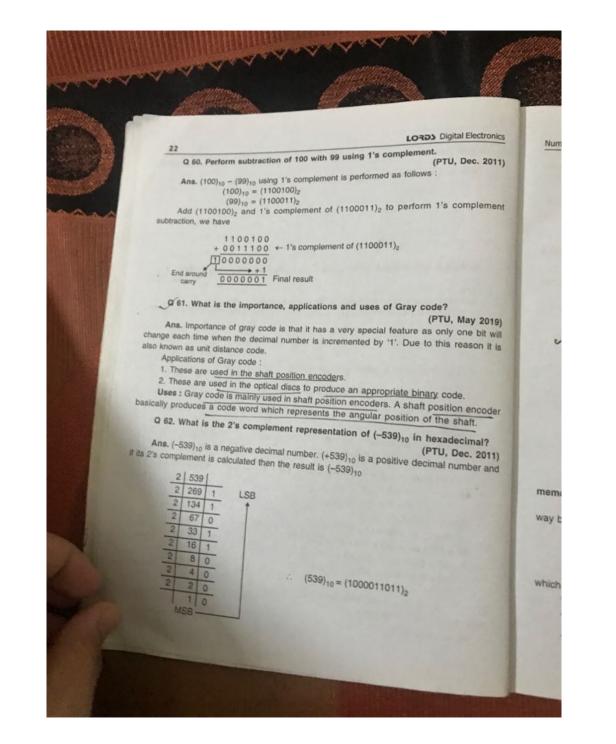

Digital Electronics Number Systems PTU, Dec. 2011) Now take 2's complement of binary data, we have 1000011011 ← Given binary data 0111100100 + 1's complement s complement 0111100101 - 2's complement Thus,  $(0111100101)_2 = (-539)_{10}$ its hexadecimal is given by Extra zero bits are added to 000111100101 complete 4-bit group  $[\because (E)_{16} = (1110)_2 = (14)_{10}]$ .: 2's complement representation of (-539)<sub>10</sub> in hexadecimal is given by J. May 2019) one bit will 63. Explain binary to gray conversion. reason it is Ans. Binary to Gray conversion is done by using following steps. (PTU, Dec. 2017) (i) Select most significant bit (MSB) and place it as it is on most significant position. (ii) Add MSB to next bit and discard carry and place it next to MSB. (iii) Add 2<sup>nd</sup> bit to 3<sup>nd</sup> bit and discard carry and write the result for other bits. de. Example : (1001)<sub>2</sub> = (?)<sub>Gray code</sub> on encoder 1001 shaft. 1111 ecimal? (1101) Gray Code )ec. 2011) : Gray code of binary (1001)2 is (1101)Gray code. umber and Q 64. What are the ways in which a negative number may be represented in the memory of a computer. (PTU, Dec. 2013) Ans. Negative number are stored as 2's complement in memory: This is the only way by which we can store -ve numbers But how does the CPU know if its -ve or +ve? Let -1 can be represented in 4 bit binary as (2's comp) 1111. 15 is also represented as 1111. So how CPU difference -1 and 15, the way to difference -1 and 15 is only the opcode which are used to do operations. Q 65. Given that  $(79)_{10} = (142)_b$  determine the value of b. (PTU, Dec. 2012) Ans.  $(79)_{10} = (142)_b$  $(142)_b = (b^2 \times 1 + b^1 \times 4 + b^0 \times 2)_{10} = (79)_{10}$ Thus,  $b^2 + 4b + 2 = 79$  $b^2 + 4b - 77 = 0$

```

Digital Electronics

umber + 33 and -33

Number Systems

(PTU, May 2005)

Q 57. Divide (10101011)<sub>2</sub> by (101)<sub>2</sub>.

33

(PTU, May 2011)

Ane. 101)10101011(10001.00101

101

0000101

101

1000

nethod.

110

(PTU, Dec. 2009)

101

Q 58. If A = 1010 and B = 1001, find A - B using 2's complement method.

(PTU, May 2011)

Ans. A = 1010, B = 1001

A-B using 2's complement subtraction is given by steps as follows:

(i) Calculate 2's complement of smaller number. The 2's complement of B is given by

0110

+1

0111

(ii) 2's complement is added to larger number

0111

1010 larger number

1 0001

Discard carry

(iii) Carry comes discard it, we get

(PTU, May 2010)

(0001)2 as a final result.

Q 59. Prove that if A + B = A + C and A' + B = A' + C, then B = C. (PTU, Dec. 2009)

A+B=A+C

....(1)

A' + B = A' + C

...(2)

Multiply (1) and (2), we get

(A + B) (A' + B) = (A + C) (A' + C)

PTU, Dec. 2010)

AA' + AB + BA' + BB = AA' + AC + CA' + CC

(: BB = B & CC = C)

0 + AB + BCA' + B = 0 + AC + CA' + C

AB + B(A' + 1) = AC + C(A' + 1)

( : A' + 1 = 1)

AB + B = AC + C

B(A + 1) = C(A + 1)

(\cdot : A + A = 1)

B = C

ec. 2014, 2010)

Hence proved.

It is used in the

```

Number which o

has a s

```

(111111000)_2 + (00010010)_2 = (00001010)_2

(-8)_{10} + (18)_{10} = (10)_{10}

(v) 12 - (-19)

(12)_{10} = (00001100)_2

(+19)<sub>10</sub> = (00010011)<sub>2</sub>

11101100 ← 1's complement

+1

(-19)<sub>10</sub> = 11101101 ← 2's complement

00001100

+ (2's complement of 1 1 1 0 1 1 0 1 ) ← (-19)<sub>10</sub>

0 0 0 1 0 0 1 0 ← 1's complement of (-19)<sub>10</sub>

+1

0 0 0 1 0 0 1 1 ← 2's complement of (-19)10

Thus, we have

00001100

+00010011

00011111 + (+31)10

12 - (-19) = (+31)10-

```

Q 67. What is the difference between 1's and 2's complement? Which is better of the two for the representation of the negative numbers and why? (PTU, Dec. 2012) Ans. 1's complement of a binary number is simply replacing all 0's by 1's and all 1's by 0's

For example: 1's complement of (10110)2 is

1 0 1 1 0 1 1 1 1 1

AND MANAGEMENT OF THE PARTY OF

0 1 0 0 1 ← 1's complement

2's complement of a binary number is one increment of 1's complement. For example : 2's complement of (10110)2 is

1 0 1 1 0 + + + 1 1 0 1 0 0 1 ← 1's complement + 1 0 1 0 1 0 ← 2's complement

2's complement is better for the representation of negative numbers because it allows so to perform the operation of subtraction by actually performing addition. It means that same circuit in a digital computer can be used for both addition and subtraction, thus it saves

A se. What do you mean by weighted code? Give example. (PTU, May 2018, 2013) Ans. Weighted codes are those codes which make use of weighted sum method i.e.

(iv) -8 + (18)

Discard carry

```

-4±18

2

```

erations

, 2012)

```

Add the larger number to it, we have

00010001

Discard carry + 1 1 1 1 1 0 1 0

100001011

(00010001)_2 = (00000110)_2 = (00001011)_2

(17)_{10} - (6)_{10} = (11)_{10}

(iii) -18 - 16

(+18)_{10} = (00010010)_2

1 1 1 0 1 1 0 1 ← 1's complement

(-18)<sub>10</sub> = 1 1 1 0 1 1 1 0 ← 2's complement

(+16)_{10} = (00010000)_2

1 1 1 0 1 1 1 1 1 ← 1's complement

(-16)<sub>10</sub> = 1 1 1 1 0 0 0 0 ← 2's complement

Thus, -18 - 16 is given by :

11101110

Discard carry + 1 1 1 1 0 0 0 0

11011110

For true value calculate 2's complement of (11011110)2

(11011110)2

0 0 1 0 0 0 0 1 ← 1's complement

+1

0 0 1 0 0 0 1 0 ← 2's complement

Thus, true value is (-00100010)2

(-18 - 16)_{10} = (-34)_{10}

```

$(+8)_{10} = (00001000)_2$

(-8)<sub>10</sub> = 1 1 1 1 1 0 0 0 ← 2's complement

11111000

1 00001010

$(+18)_{10} = (00010010)_2$

1 1 1 1 0 1 1 1 ← 1's complement

$$b = \frac{-4 \pm \sqrt{16 - 4.1 (-77)}}{2} = \frac{-4 \pm \sqrt{16 + 308}}{2} = \frac{-4 \pm \sqrt{324}}{2} = \frac{-4 \pm 18}{2}$$

$$b = \frac{-4 + 18}{2} \text{ or } b = \frac{-4 - 18}{2}$$

$$= \frac{14}{2} = 7 \text{ or } b = \frac{-22}{2} = -11 \text{ (Not possible)}$$

Q 66. Using 2's complement notation perform the following arithmetic operations

(i) 25 + (-12) (ii) 17 - 6 (iii) -18 - 16 (iv) -8 + (18) (v) 12 - (-19) (PTU, Dec. 2013, 2012)

Ans. (i) 25 + (-12)  $(25)_{10} = (11001)_2 = (00011001)_2 \leftarrow \text{Larger number}$  $(12)_{10} = (1100)_2 = (00001100)_2 \leftarrow \text{Smaller number}$ 25 + (-12) => 25 - 12 00011001 ← Larger number -00001100 ← Smaller number

2's complement of smaller number (00001100)2 is given by 11110011 ← 1's complement + 1

Add the larger number to it, we have

00011001 ← larger number Discard carry + 1 1 1 1 0 1 0 0 ← 2's complement of smaller number 1000001101

$(00011001)_2 - (00001100)_2 = (00001101)_2$ 25 + (-12) = 13. (ii) 17 - 6

$$(17)_{10} = (10001)_2 = (00010001)_2$$

$(6)_{10} = (110)_2 = (00000110)_2$

2's complement of smaller number (00000110)<sub>2</sub> is given by 11111001 ← 1's complement

Q 77. What is the difference between digital and binary ? Ans. Digital is discrete data where as binary means two bits '0' and '1'. Digital signals make use of binary information or data or bits. Digital signal is represented by using binary

Q 78. Convert the following numbers :

(a)

$$(12.25)_{10} = (?)_2$$

(b)

$$(10101.1101)_2 = (?)_8$$

(e)  $(67.2)_8 = (?)_2$

(c)

$$(125)_8 = (?)_{10}$$

(d)  $(34)_{16} = (?)_2$ Ans. (a)  $(12.25)_{10} = (?)_2$

(b)  $(10101.1101)_2 = (?)_8$

(PTU, Dec. 2016)

$(12)_{10} = (1100)_2$  $(0.25)_{10} = (.01)_2$

010101.110100

$(12.25)_{10} = (1100.01)_2$

$(125)_8 = (?)_{10}$ (c)  $1 \times 8^2 + 2 \times 8^1 + 5 \times 8^0 = 64 + 16 + 5 = (85)_{10}$

(d)  $(34)_{16} = (?)_2$  $(0011\ 0100)_2 = (110100)_2$

$(67.2)_8 = (?)_2$

### Q 79. Evaluate Following:

(a) Multiply 2A816 by B616

(b) Subtract '14 from 46 using 8 bit 2's complement arithmetic. (PTU, May 2018)

Ans. (a)

$8 \times 6 = (48)_{10} = (30)_{16}$  $(10 \times 6) + 3 = (63)_{10} = (3F)_{16}$  $(11 \times 8) = (88)_{10} = (58)_{16}$  $(11 \times 10) + 5 = (115)_{10} = (75)_{16}$  $(11 \times 12) + 7 = (29)_{10} = (1D)_{16}$ : (2A8)<sub>16</sub> × (B6)<sub>16</sub> = (1E570)<sub>16</sub>

I (b) Subtract 14 from 46:

$(46)_{10} = (1110)_2 = (00011110)_2$  for 8-bit data  $(14)_{10} = (1110)_2 = (00001110)_2$  for 8 bit data.

Calculate 2's complement of smallest number, we get

00001110 1 1 1 0 0 0 0 1 ← 1's complement + 1

11100010 ← 2's complement

Add above in largest number, we get

11100010 00101110 (1)00010000

Discard/

$(00010000)_2 = (32)_{10}$

which obey the principle of positional weight. In weighted codes each position of the number

- Weighted codes are :

- 1. Binary codes

- 2. BCD codes. For example : 8421, 2421, 4221, 5311, 7421, 8421 etc.

- Q 69. Convert the following decimal numbers to binary

Ans.

(PTU, Dec. 2013)

(i) 104

| 2 | 104 |   |     |

|---|-----|---|-----|

| 2 | 52  | 0 | LSE |

| 2 | 26  | 0 | 1   |

| 2 | 13  | 0 |     |

| 2 | 6   | 1 |     |

| 2 | 3   | 0 |     |

| 2 | 1   | 1 |     |

$$\therefore$$

(104)<sub>10</sub> = (1101000)<sub>2</sub>

(ii) 1998

7 1

- Q 70. Subtract the following binary numbers using 2's compliment

- (i) 11010-1101 (ii) 10010-10011 Ans.

(PTU, Dec. 2013)

(i) 11010-1101

minuend = 11010

Subtrahend = 1101 2's compliment of subtrahend, 1101 is

0010 +1 0011

Now add minuend, 11010 to 0011

11010 0011 11101

Hence Final result = (11101)<sub>2</sub>

(ii) 10010-10011

minuend = 10010 Subtrahnend = 10011

2's compliment of subtrahnend 10011 is

01100 4 +1 01101

Now add minuend, 10010 to 01101

10010 01101 11111

Hence Final result = (1111)2

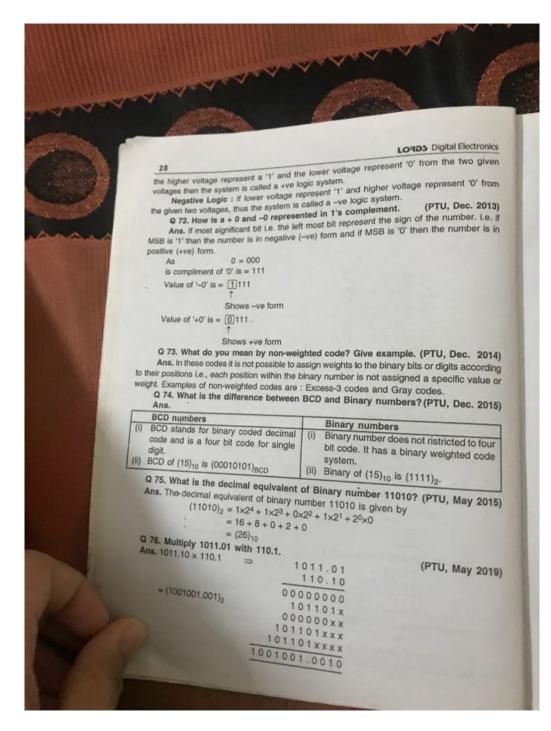

Q 71. What is meant by positive and negative logic?

(PTU, Dec. 2013)

Ans. Positive Logic: As two voltage level represent the two binary digits '1' and '0'. If

hat es

WS

ter of

2012)

y 0's.

13)

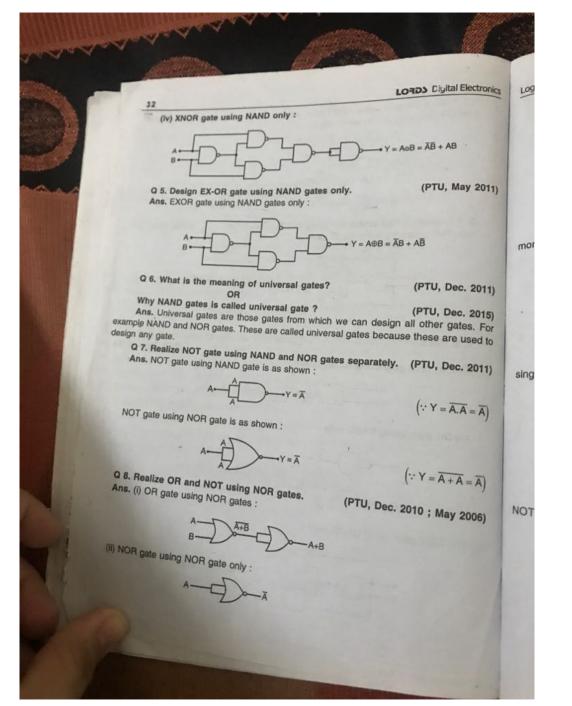

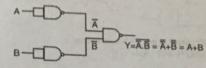

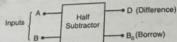

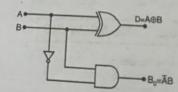

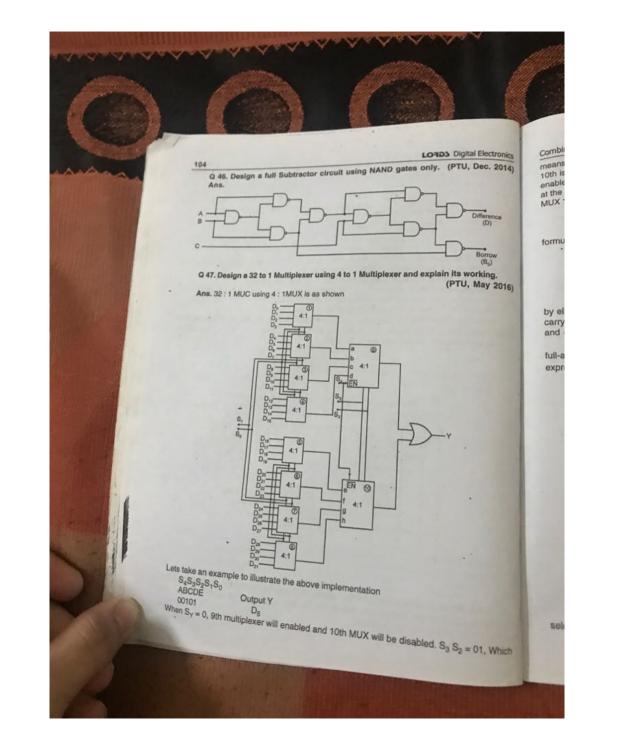

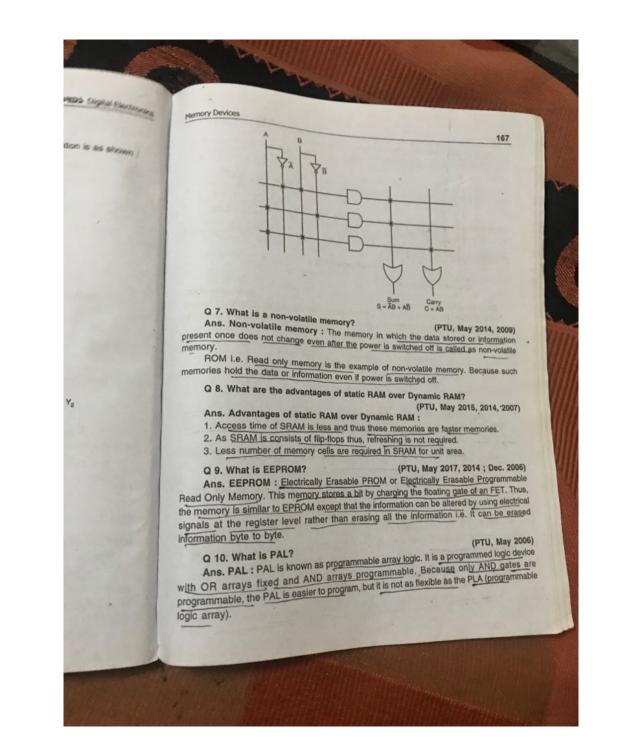

Q 2. Realize OR gate using NAND gates only.

Ans. OR gate using NAND gates only;

(PTU, May 2007)

$$Y = \overline{A.B} = \overline{A} + \overline{B} = A + B$$

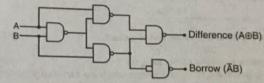

Q 3. Implement half subtractor using NAND gates.

Ans. Half subtractor using NAND gates :

(PTU, May 2010)

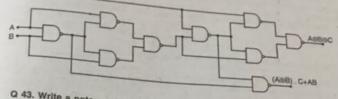

Q 4. Realize AND, OR, X-OR, X-NOR gates with the help of only NAND gates.

(PTU, Dec. 2010)

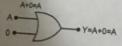

Ans. (i) AND gate using NAND Only:

$$A \longrightarrow A \longrightarrow AB = AB$$

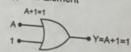

(ii) OR gate using NAND only:

(iii) XOR gate using NAND only:

$$A = \overline{A}B + A\overline{B}$$

ates

Logic

DR.

ts and

ersa.

from

07)

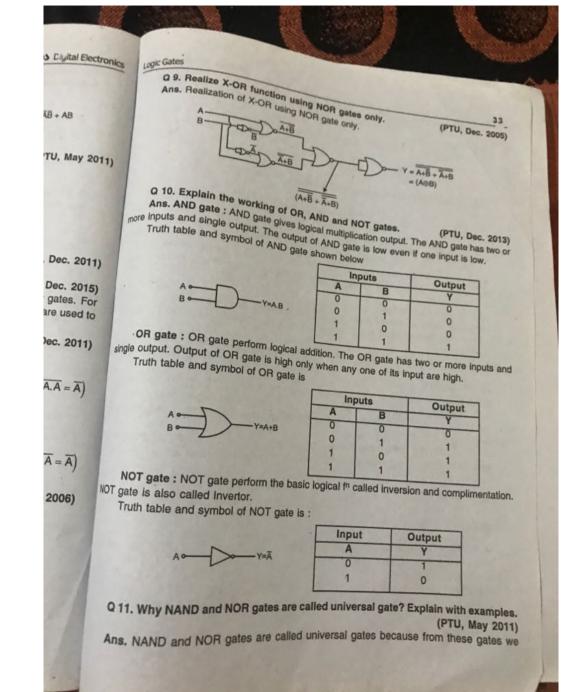

### Chapter

Andre Andrew

### **Logic Gates**

#### Contents

AND, OR, NOT, NAND, NOR, Exclusive-OR and Exclusive-NOR. Implementations of Logic Functions using gates, NAND-NOR implementations.

### POINTS TO REMEMBER

- Logical gates most commonly used are AND, OR, NOT, NAND, NOR, XOR, XNOR.

- NAND and NOR are universal gates.

- Output of AND gate is low even if one input is low (Y = A.B) where A and B are inputs and Y is the output.

- Ear Output of OR gate is high if any one input is high (Y = A + B).

- In NOT gate, when a high is applied as input, a low appears at output and vice versa.

- NAND gate has output high when any one of its input is low.

- The output of NOR gate is high when any input is low.

- Output of XOR gate is high if one and only one input is high.

- The output of XNOR gate is high when all inputs are high.

- NAND and NOR can be used to realize any gate.

- Propagation delay is the average transition delay time for a pulse to propagate from

## QUESTION-ANSWERS

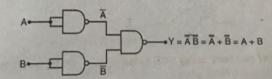

Q 1. Realize AND gate using NOR gates only.

(PTU, May 2015; Dec. 2016, 2007)

$$A - D - \overline{A}$$

$$\overline{A} + \overline{B} = \overline{A}.\overline{B} = A.B$$

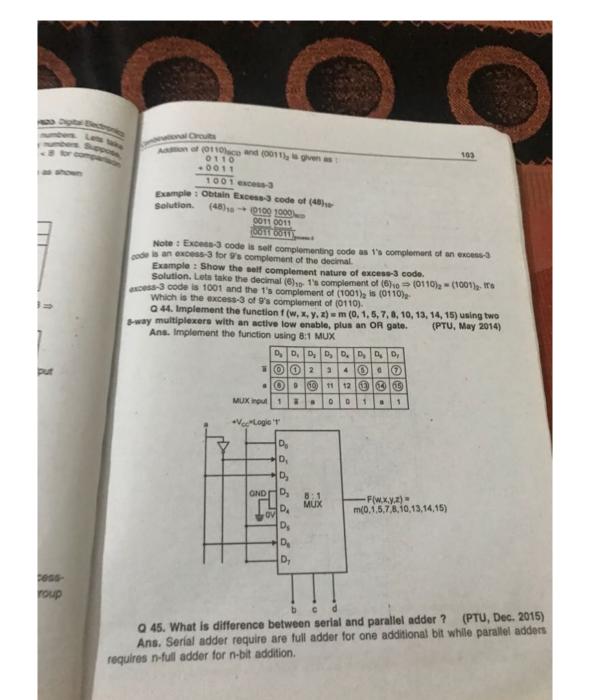

Bechanics dissign or Unife Gates. at guines. Q 17. Exclusive NOR versus Exclusive OR Ans. Exclusive NOR (PTU, May 2018) Exclusive OR (f) Symbol: (i) Symbol: A (I) Y=AOB= AB+AB (6) Y = A0B = AB+AB (III) AOB = AGB BOA = BOA (W) Q 18. Number of Gate inputs required for expression ABC+ABCD+EF+AD. Ams. ABC+ABCD+EF+AD (PTU, May 2018) = ABC+EF+AD(BC+1) 2013) - ABC+EF+AD Fine logic gates are required and six inputs are required. on with of their 000 sed to use of 2014) 2015) 图 地 nting 017) 17)

can implement any other gate. Thus, by using NAND and NOR gates one can design or implement other gates like AND, OR, XOR, XNOR, NOT or any combination of basic gates.

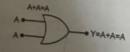

(i) Implementation of AND gate using NAND gates only is as shown:

(ii) Implementation of OR gate using NOR gates only in as shown

$$A \longrightarrow A + B$$

$$B \longrightarrow A + B = A + B$$

### Q 12. What is a truth table? How is it represented? What are its uses?

(PTU, Dec. 2013)

Ans. Truth table is a mathematical table used in logic, specifically in connection with Boolean Algebra to compute the functional value of logical expressions on each of their functional arguments.

Truth-table is represented in a tabular (table) form.

Uses : In digital electronics and computer science engg., truth tables can be used to reduce basic boolean operations to simple correlation of input to outputs without the use of logic gates or code.

Q 13. How many AND gates are required to realize Y = ACD + EF + GH.

Ans. Three AND gate are required.

(PTU, May 2014)

Q 14. Which Gate is a single input gate and why?

Ans. NOT gate is a single input gate. It has to complement the given input. Thus, if '1' is provided at the input '0' will be produced at output and vice-versa. It is used for complementing

Q 15. Explain the NOR Gate. Specify its symbol.

(PTU, May 2017)

Ans. NOR gate is the combination of OR and NOT gates. Its symbol is

Also,  $Y = \overline{A} + \overline{B}$

Q 16. Write the applications of EX-OR gate. Ans. Applications of XOR gate

1. Arithmetic operations 2. Parity checker

3 Binary of gray code conversion

4. Gray to binary code conversion 6. Digital comparator

(PTU, May 2017)

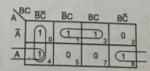

2. Three Variable K-map :  $2^n = M'$  formula is used i.e.  $2^3 = 8$ . It means a '3' variable K-map consists of '8' squares as shown:

| N    | BC BC | BC  | BC  | BÖ  |    | AB | 00  | 01  | 11  | 10  |

|------|-------|-----|-----|-----|----|----|-----|-----|-----|-----|

|      |       | 1   | 1   | ĀBĒ |    | 0  | 000 | 001 | 011 | 010 |

| A    | ABC   | AEC | ABC | ABĒ | OR | 1  | 100 | 101 | 111 | 110 |

| - 33 |       |     | -   |     |    |    |     |     |     |     |

K-Map for 3-variables

| . Decimal<br>Number |   | Varial<br>B |   | Minterms<br>Designation | Minterm        | Maxterms<br>Designation                      | Maxterm        |

|---------------------|---|-------------|---|-------------------------|----------------|----------------------------------------------|----------------|

| 0                   | 0 | 0           | 0 | ĀBC                     | Mo             | A+B+C                                        | Mo             |

| 1                   | 0 | 0           | 1 | ĀBC                     | M <sub>1</sub> | A+B+C                                        | M <sub>1</sub> |

| 2                   | 0 | 1           | 0 | ĀBĒ                     | M <sub>2</sub> | A+B+C                                        | M <sub>2</sub> |

| 3                   | 0 | 1           | 1 | ĀBC                     | M <sub>3</sub> | $A + \overline{B} + \overline{C}$            | M <sub>3</sub> |

| 4                   | 1 | 0           | 0 | ABC                     | M <sub>4</sub> | A+B+C                                        | M <sub>4</sub> |

| 5                   | 1 | 0           | 1 | ABC                     | M <sub>5</sub> | A+B+C                                        | Ms             |

| 6                   | 0 | 1           | 1 | ABC                     | M <sub>6</sub> | A+B+C                                        | Me             |

| 7                   | 1 | 1           | 1 | ABC                     | M <sub>7</sub> | $\overline{A} + \overline{B} + \overline{C}$ | M <sub>7</sub> |

### Truth Table for 3-variable K-map

3. Four Variable K-map

Formula used is  $2^n = M$

Where, n = number of variables, M = Number of squares

n = 4

$2^4 = 16$

So, '4' variable K-map consists of '16' squares.

| AB | CD CD | ČD   | CD   | CD   |

|----|-------|------|------|------|

| ĀB | ĀBCD  | ĀBĒD | ĀBCD | ĀBCŌ |

| ĀB | ĀBĒŌ  | ĀBĒD | ĀBCD | ĀBCĪ |

| AB | ABCD  | ABCD | ABCD | АВСБ |

| AB | ABCD  | ABCD | ABCD | ABCD |

| ABCI | 00 | 01 | 11 | 10 |

|------|----|----|----|----|

| 00   | 0  | 1  | 3  | 2  |

| 01   | 4  | 5  | 7  | 6  |

| 11   | 12 | 13 | 15 | 14 |

| 10   | 8  | 9  | 11 | 10 |

4-Variable K-map

ninterms (m). s (M). unction. It is able. -map. Here.

rwise. e formed in

tion. When

er Boolean

13, 2009)

(ii)  $\overline{A.B} = \overline{A} + \overline{B}$

It states that  $\overline{A} + \overline{B}$  is the complement of A . B.

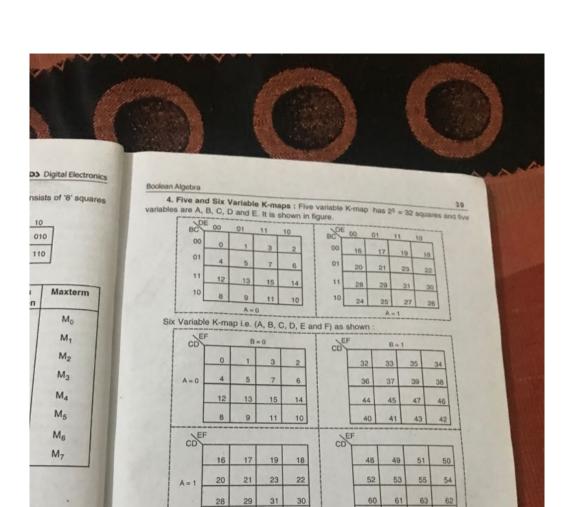

Q 2. What is K-map? Why we need K-maps? Give the various types of K-map.

Ans. K-map i.e. Karnaugh map is simply a graphical method for representing a Boolean function. The Karnaugh map is a systematic method for simplify and manipulating Boolean expression. It is used to simplify a logic expression or to convert a truth table to its corresponding logic circuit. It is used for the minimization of switching functions but upto 'six' variables. For more than 'six' vairable it becomes complex or cubersome.

The K-map for n-Boolean variable switching function consists of '2n' squares. Here each square represents the normal or standard term i.e. one minterm or maxterm.

Need of K-maps: We need K-map for representing Boolean function through graphical method. Because K-map simplify and manipulates a Boolean expression. So to solve or simplify a Boolean expression, we use K-map. K-map can be used for problems involving any number of input variables (upto six variables) which is not easily solve by Boolean Algebra.

Types of K-map: Types of K-maps commonly used are

- 1. Two variable K-map

- 2. Three variable K-map

- 3. Four variable K-map

- 4. Five variable K-map

- 5. Six variable K-map

- 1. Two variable K-map:

2n = M formula is used where, n = Number of variables and M = Number of squares. Thus,  $2^2 = 4$

: '2' variable K-map consists of '4' squares. It is shown in figure.

| A | B .              | В                | AB | B              | В              |

|---|------------------|------------------|----|----------------|----------------|

| Ā | ĀB₀₀             | ĀB <sub>01</sub> | Ā  | Mo             | M <sub>1</sub> |

| A | AB <sub>10</sub> | AB <sub>11</sub> | A  | M <sub>2</sub> | M <sub>3</sub> |

| В              |   |  |

|----------------|---|--|

| M <sub>1</sub> | 1 |  |

| Мз             | 1 |  |

|                | - |  |

37

K-map for Minterms

K-map for Maxterms

### Truth Table for Maxterms and Minterms

| Decimal | Variables |    | Minterm     | Minterm        | Maxterms    | Maxterm        |  |

|---------|-----------|----|-------------|----------------|-------------|----------------|--|

| Number  | A B       |    | Designation |                | Designation |                |  |

| 0       | 0         | 0  | ĀB          | Mo             | A+B         | Mo             |  |

| 1       | 0.        | -1 | ĀB          | M <sub>1</sub> | A+B         | M <sub>1</sub> |  |

| 2       | 1         | 0  | AB          | M <sub>2</sub> | Ā+B         | M <sub>2</sub> |  |

| 3       | 1         | 1  | AB          | МЗ             | A+B         | M <sub>3</sub> |  |

### Chapter

## **Boolean Algebra**

ex

CO

va

ea

m sir

#### Contents

Boolean postulates and laws - De-Morgan's Theorem, Principle of Duality, Boolean expression - Boolean function, Minimization of Boolean expressions - Sum of Products (SOP), Product of Sums (POS), Minterm, Maxterm, Canonical forms, Conversion between canonical forms, Karnaughanap Minimization, Don't care conditions, Quine-McCluskey method.

## POINTS TO REMEMBER

- SOP involves sum of given product terms and these terms are known as minterms (m).

- POS involves product of given sum terms of these are known as maxterms (M).

- A karnaugh map is simply a graphical method for representing a boolean function. It is used to simplify a logic equation on to convert a truth table to its logic circuit.

- Types of K-map are 2 variable, 3 variable, 4 variable, 5 variable and 6 variable.

- Ear 2n = M formula is used for the calculation of total number of squares in a K-map. Here, n=number of variables and M = number of squares.

- For representing SOP form for K map; enter 1 for each minterm and 0 otherwise.

- To minimize the boolean expression using K-map, pair, Quad and octet are formed in increasing priority.

- Duality

- G-M method in the Quine-McCluskey method or tabular method for minimization. When variables are more than six then K-map is cumber same.

- Duality Theorem : According to Duality theorem, from one Boolean relation ofher Boolean

- (a) Changing each OR sign to an AND sign,

- (b) Changing each AND sign to an OR sign,

- (c) Complementing any '0' or '1' present in the expression.

# QUESTION-ANSWERS

Q 1. State De-Morgans theorem. Ans. De-Morgan's Theorem are :

(PTU, May 2016, 2013, 2009)

(1)  $\overline{A+B} = \overline{A} \cdot \overline{B}$

It states that  $\overline{A}$ ,  $\overline{B}$  is the complement of A+B.

$$\because (\overline{A} + A = 1)$$

### Boolean Algebra

Using boolean,  $Y = \overline{A}BC + \overline{A}B\overline{C}$

$$Y = \overline{A}B.1 = \overline{A}B$$

·· (C+C=1)

.. Minimized output of K-map is  $Y = \overline{A}$ . B (ii) F (A, B, C) =  $\Sigma m$  (1, 3, 5, 7)

Y=C

Using boolean,  $Y = \overline{A}\overline{B}C + \overline{A}BC + A\overline{B}C + ABC$

$$= \overline{A}C(\overline{B}+B)+AC(\overline{B}+B)$$

$(: \overline{B} + B = 1)$

$$Y = \overline{A}C + AC = C(\overline{A} + A) = C$$

: Minimized output of K-map is Y = C (iii) F (A, B, C) =  $\Sigma$ m (0, 4, 1, 3, 6)

$Y = \overline{A}C + \overline{B}\overline{C} + AB\overline{C}$

Using boolean,  $Y = \overline{A}\overline{B}\overline{C} + A\overline{B}\overline{C} + \overline{A}\overline{B}C + \overline{A}BC + \overline{A}BC$

$$= \left(\overline{A} + A\right) \overline{B} \overline{C} + \left(\overline{B} + B\right) \overline{A} C + A B \overline{C}$$

=

$$\overline{BC}.1+\overline{AC}.1+\overline{ABC}$$

$$Y = \overline{B}\overline{C} + \overline{A}C + AB\overline{C}$$

So minimized value of K-map is  $Y = \overline{AC} + \overline{BC} + AB\overline{C}$

$(\overline{A} + A = 1)$

Using boolean,  $Y = \overline{A}B + AB$

= B. 1 = B Y = B, is the simplified expression.

(ii)  $F(A, B) = \Sigma m(0, 2)$

$Y = \overline{B}$

Using boolean,  $Y = \overline{A}\overline{B} + A\overline{B}$

$$=\overline{B}\left(\overline{A}+A\right)$$

$\therefore Y = \overline{B}$ (iii)  $F(A, B) = \Sigma m (1, 2)$

| 12 P | 0   | 8  |

|------|-----|----|

| Ā    | 0 0 | 1, |

| A    | 1 2 | 0  |

$$Y = \overline{A}B + AB$$

It is the simplified expression.

Grouping of 3 variable K-map.

Q 4. Solve following using K-map and boolean algebra : (i) F (A, B, C) =  $\Sigma m$  (2, 3)

(1)

$$F(A, B, C) = \Sigma m (2, 3)$$

(ii)

$$F(A, B, C) = \Sigma m (2, 3)$$

(iii)  $F(A, B, C) = \Sigma m (1, 3, 5, 7)$

(ii)

$$F(A, B, C) = \Sigma m (1, 3, 5, 7)$$

(iii)  $F(A, B, C) = \Sigma m (0, 4, 1, 3, 6)$

Solution. (i)  $F(A, B, C) = \Sigma m (2, 3)$

| AB | C BC | ВC  | BC  | ⊼a  |

|----|------|-----|-----|-----|

| Ā  | 0 0  | 0 , | 1   |     |

| A  | 0 4  | 0 5 | 0 7 | 0 8 |

Y = AB

Grouping of 2 variable K-map.

Q 3. Solve following using K-map and boolean algebra :

27

25

- (i)  $F(A, B) = \Sigma m(1, 3)$

- (ii)  $F(A, B) = \Sigma m(0, 2)$

- (iii)  $F(A, B) = \Sigma m(1, 2)$

Solution. (i)  $F(A, B) = \Sigma m(1, 3)$

Y=B

(PTU, Dec. 2006)

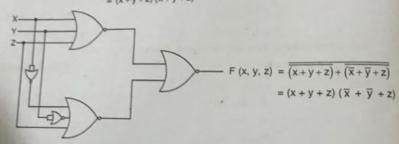

Q 8. Implement the function F (x, y, z) =  $\Sigma$  (0, 6) with NOR gates.

Ans.

$$F(x, y, z) = \Sigma \pi (0, 6)$$

| N. | yz  | yz  | yz  | yz  |

|----|-----|-----|-----|-----|

| X  | 1 0 | 0,  | 0 3 | 0 2 |

| x  | 0 4 | 0 8 | 0 7 | 1 6 |

$$F(x, y, z) = (x + y + z) (\overline{x} + \overline{y} + z)$$

By using NOR gates we have to use demorgan law :

$$\stackrel{=}{F}(x, y, z) = \overline{(x+y+z)(\overline{x}+\overline{y}+z)}$$

$$= \overline{(x+y+z)(\overline{x}+\overline{y}+z)}$$

### Q 9. What is don't care condition?

(PTU, Dec. 2015; May 2006)

Ans. Don't Care Condition: Don't care conditions are used in K-maps. There may be cases in which the output for certain input combinations has no effect on overall output. Such conditions are known as don't care conditions. In don't care terms, output can be considered as 0' or '1' and it is designated by 'd' or 'φ' or 'X'. For K-map simplification 'X' can be taken as "O' or '1' so that it gives the minimized output expression.

Q 10. Convert the following logic function in a product of max terms. F (A, B, C) = (A' + B) (B' + C).(PTU, Dec. 2005)

As,

$$A + BC = (A + B) (A + C)$$

$$(A' + B + CC')(B' + C + AA')$$

can be written as

$$F(A, B, C) = (A' + B + C) (A' + B' + C') (B' + C + A) (B' + C + A')$$

tronics

:

Boolean Algebra

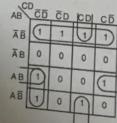

(iii) F (A, B, C, D) =  $\Sigma$ m (0, 1, 4, 5, 3, 2, 11, 10) Solution.

| AB | do c | ČD   | CD   | CDI |

|----|------|------|------|-----|

| ĀB | 1 0  | 1).  | 1    | 1   |

| ĀB | 1    | 1)5  | 0    | 0   |

| AB | 0 12 | 0 13 | 0 15 | 0.4 |

| AB | 0 8  | 0 9  | 1 ,  | 1)  |

|    |      |      |      | 10  |

$Y = \overline{AC} + \overline{BC}$

Using boolean,  $Y = \overline{AC} + \overline{ABC} + \overline{ABC}$

$$= \overline{AC} + (\overline{A} + A) \overline{BC}$$

$$= \overline{AC} + \overline{BC} \cdot 1$$

$$Y = \overline{AC} + \overline{BC}$$

Q 6. Using boolean algebraic theorems, prove that

$$A + \overline{A}B + A\overline{B} = A + B$$

(PTU, Dec. 2007)

Ans.

$$A + \overline{A}B + A\overline{B}$$

=  $A + B + A\overline{B}$  (  $\therefore A + A\overline{B} = A + B$ )

$$= B + A (1 + \overline{B})$$

$$= B + A \cdot 1 \Rightarrow A + B$$

$(\cdot \cdot 1 + \overline{B} = 1)$

L.H.S = R.H.S hence, proved.

Q 7. Define De-Morgan's theorem.

(PTU, Dec. 2012, 2009; May 2007)

Ans. De Morgans Theorem :

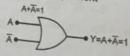

Theorem 1. It states that NAND gate can be replaced by bubbled OR gate.

i.e.

$$\overline{A.B.C} = \overline{A} + \overline{B} + \overline{C} + \dots$$

$$\frac{A}{B} \longrightarrow_{\overline{Y} = \overline{A} \overline{B}} \Rightarrow \longrightarrow_{\overline{Y} = \overline{A} + \overline{B}} \Rightarrow \frac{A}{B} \longrightarrow_{\overline{Y} = \overline{A} + \overline{B}}$$

Theorem 2. It states that NOR gate can be replaced by bubbled AND gate.

i.e.

$$\overline{A+B+C}+.....=\overline{A}.\overline{B}.\overline{C}...$$

Boole

Grouping of 4 variable K-map. Q 5. Solve the following using K-map and verify by using boolean algebra : (i) F (A, B, C, D) =  $\Sigma$ m (3, 4, 5, 7, 9, 13, 14, 15) Solution.

| 10 | D ZĐ | ĒD   | CD   | CĎ   |

|----|------|------|------|------|

| AB | 0    | 0,   | 1 3  | 0 2  |

| ĀB | 1    | 1    | 1,   | 0 6  |

| AB | 0 12 | 17,3 | 1,5  | 1)4  |

| AB | 0 8  | 19   | 0 11 | 0 10 |

$Y = \overline{A}CD + \overline{A}B\overline{C} + A\overline{C}D + ABC$

Using boolean,

$$Y = \overline{A}\overline{B}CD + \overline{A}\overline{B}CD + \overline{A}\overline{B}\overline{C}\overline{D} + \overline{A}\overline{B}\overline{C}D$$

$$= \overline{A}CD(\overline{B} + B) + \overline{A}B\overline{C}(\overline{D} + D) + A\overline{C}D(B + \overline{B}) + ABC(D + \overline{D})$$

$$Y = \overline{A}CD + \overline{A}B\overline{C} + A\overline{C}D + ABC$$

(ii) F (A, B, C, D) =  $\Sigma m$  (0, 1, 2, 3, 6, 8, 9, 10, 11, 12, 13) Solution.

| AB | DICD | ĈD   | CD   | CDI  |

|----|------|------|------|------|

| ĀB | 1    | 1    | 1    | 1    |

| ĀB | 0 4  | 0 5  | 0 7  | 1 6  |

| AB | 1 12 | 1 13 | 0    | 0    |

| AB | 1    | 1 9  | 1 11 | 1 10 |

$Y = \overline{B} + A\overline{C} + \overline{A}C\overline{D}$

Using boolean,

$$Y = \overline{A}\overline{B} + A\overline{B} + \overline{A}C\overline{D} + AB\overline{C}$$

$$= \overline{B}(\overline{A} + A) + \overline{A}C\overline{D} + AB\overline{C}$$

$$Y = \overline{B} + \overline{A}C\overline{D} + AB\overline{C}$$

$$= \overline{B} + A\overline{C} + \overline{A}C\overline{D}$$

$(\overline{B} + AB\overline{C} = \overline{B} + A\overline{C})$

09) 1) B)

```

LORDS Digital Electronics

```

```

(PTU, May 2009)

Q 14. Prove that if A + B = A + C and AB = AC then B = C.

(: B.1 = B and 1 + A = 1)

(: B.B = B)

B = B (1 + A)

Ans.

= B + BA = B.B + BA

= B (B + A) = B (A + B)

A + B = A + C (Given)

B = B (A + C)

= AB + BC

A.B = A.C (Given)

But

B = AC + BC

= C (A + B)

A + B = A + C (Given)

But

B = C(A + C)

( .. C.C = C)

= AC + C.C = AC + C

(: A+1 = 1)

= C (A + 1)

B = C

Hence, proved.

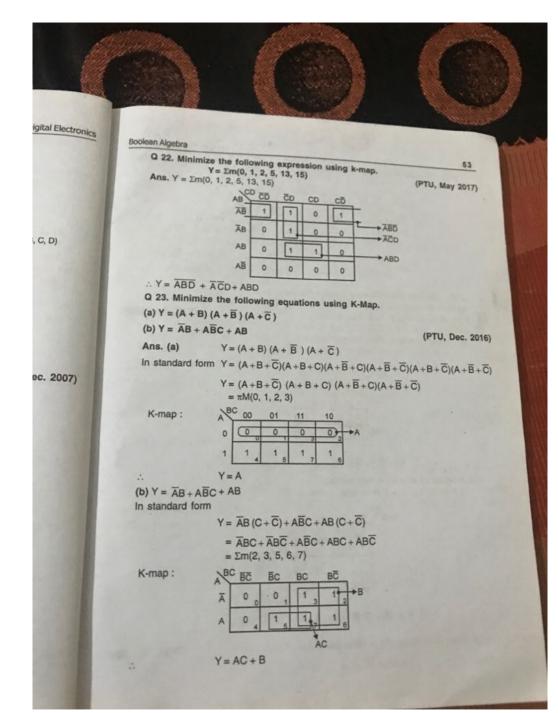

Q 15. Reduce the following equation using k-map

Y = ABC+ACD+AB+ABCD+ABC.

(PTU, Dec. 2008)

Ans. Y = \overline{A}\overline{B}\overline{C} + A\overline{C}\overline{D} + A\overline{B} + ABC\overline{D} + \overline{A}\overline{B}C

```

Firstly, convert the output Y to its standard SOP form, we have

$$Y = \overline{ABC}(D+\overline{D}) + A(B+\overline{B})\overline{CD} + A\overline{B}(C+\overline{C})(D+\overline{D}) + ABC\overline{D} + \overline{ABC}(D+\overline{D})$$

$$= \overline{ABCD} + \overline{ABCD} + AB\overline{CD} + AB\overline{CD} + (A\overline{BC} + A\overline{BC})(D + \overline{D})$$

=

$$\overline{ABCD} + \overline{ABCD} + AB\overline{CD} + A\overline{BCD} + A\overline{BCD} + A\overline{BCD}$$

Y =

$$\overline{ABCD} + \overline{ABCD} + \overline{ABCD}$$

$Y = \overline{AB} + A\overline{CD} + AB\overline{D} + \overline{BCD}$  is the reduced expression using k-map.

(PTU, Dec. 2004)

(900)

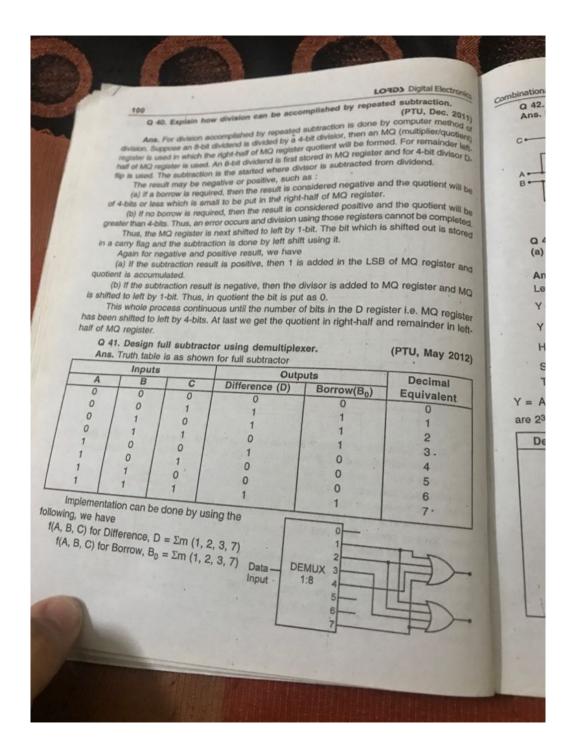

Q 11. Convert the following logic function in a product of maxterns Ans. F (A, B, C, D) = C' D + ABC' + ABD' + A' B' D (PTU, May 2005) For maxterms complement the given function :

$$F(A, B, C, D) = \overline{C'D + ABC' + ABD' + A'B'D}$$

or  $\overline{CD} + AB\overline{C} + AB\overline{D} + \overline{A}\overline{B}D$

$$= (\overline{CD}) (\overline{ABC}) (\overline{ABD}) (\overline{\overline{ABD}})$$

$$= (\overline{C} + D) (\overline{\overline{A}} + \overline{\overline{B}} + \overline{C}) (\overline{\overline{A}} + \overline{\overline{B}} + \overline{D}) (\overline{\overline{A}} + \overline{\overline{B}} + \overline{D})$$

$$= (C + D) (\overline{\overline{A}} + \overline{\overline{B}} + C) (\overline{\overline{A}} + \overline{\overline{B}} + D) (\overline{\overline{A}} + \overline{\overline{B}} + \overline{D})$$

Q 12. Convert the following logic function is a product of maxterms

Max term can be given as:

$$\overline{DA'+DB+B'D}$$

$$= (\overline{DA'})(\overline{DB})(\overline{B'D})$$

$$= (\overline{D}+\overline{A})(\overline{D}+\overline{B})(\overline{B}+\overline{D})$$

$$(: A' = \overline{A})$$

$$F (A, B, C, D) = (\overline{D}+A)(\overline{D}+\overline{B})(B+\overline{D}).$$

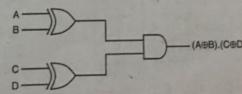

Q 13. Implement the Boolean function with exclusive -OR and AND gates : F = AB' CD' + A' BCD' + AB' C' D + A' BC' D (PTU, Dec. 2004)

F = AB' CD' + A' BCD' + AB' C' D + A' BC' D

Ans.

F = AB' CD' + A'BCD' + AB'C'D + A'B C'D

= CD' (AB' + A'B) + C'D (AB' + A'B)

= CD' (A

$$\oplus$$

B) + C'D (A  $\oplus$  B)

= (A  $\oplus$  B) (CD' + C'D)

= (A  $\oplus$  B) (C  $\oplus$  D)

(a) The Truth table from previous truth table for function F is given by

| ne Truth | Inputs | Output |   |

|----------|--------|--------|---|

|          | B      | C      | F |

| A        |        | 0      | 1 |

| 0        | 0      |        | 1 |

| 0        | 0      | 1      | 1 |

| 0        | 1      | 0      |   |

| 0        | 1      | 1      | 1 |

| .        | 0      | 0      | 0 |

| 1        | -      |        | 0 |

| 1        | 0      | 1      | 0 |

| 1        | 1      | 0      | 0 |

| 1        | 1      | 1      | 1 |

(b)  $F(A, B, C) = \overline{A} \overline{B} \overline{C} + \overline{A} \overline{B} C + \overline{A} B \overline{C} + \overline{A} B C + ABC$

is the expression for SOP form. Its simplified form is given by

$$= \overline{AB} (\overline{C} + C) + \overline{AB} (\overline{C} + C) + ABC$$

$$\left( \because \left( \overline{A} + AB \right) = \overline{A} + B \right)$$

(: C+C=1)

(c) F (A, B, C) = (A + B + C)

$$(A + B + \overline{C}) (A + \overline{B} + C) (A + \overline{B} + \overline{C})$$

( $\overline{A} + \overline{B} + \overline{C}$ ) is the expression for POS town

is the expression for POS form.

its simplified form can be calculated from SOP form and is given as

$$\overline{A} + BC = (A) (\overline{B} + \overline{C})$$

(d) For 2-input NAND gates, we have

$$F = (\overline{A})(\overline{B.C})$$

U, May 2008)

$AC = \overline{A} + C$

$+\overline{A}B=\overline{A}B$

Boolean Algebra

### (c) AB+A+AB

$$= \overline{A} + \overline{B} + \overline{A} + AB$$

$$= \overline{A} \cdot \overline{B} \cdot \overline{A} \cdot \overline{A} \cdot \overline{B}$$

$$= A \cdot B \cdot (\overline{A} + \overline{B}) \qquad (\because \overline{A} = A)$$

$$= AB\overline{A} + AB\overline{B}$$

= 0 = R.H.S.

$(: A.\overline{A} = 0, B\overline{B} = 0)$

Hence proved.

Q 19. A combinational circuit has 3 inputs A, B, C and output F. F is true for following input combinations

A is False, B is True

A is False, C is True

A, B, C are False

A. B. C are True

(a) Write the Truth Table for F. Use the convention True = 1 and False = 0.

- (b) Write the simplified expression for F in SOP form.

- (c) Write the simplified expression for F in POS form.

- (d) Draw logic circuit using minimum number of 2 input NAND gates.

(PTU, May 2008)

Ans. The functional block diagram shows the combinational circuit :

According to the given inputs the truth table is as shown

| A | В | C | F |

|---|---|---|---|

| 0 | 1 | X | 1 |

| 0 | X | 1 | 1 |

| 0 | 0 | 0 | 1 |

| 1 | 1 | 1 | 1 |

(Where X = don't care as it is not given in the question for C and B inputs)

Thus, from (1) and (2) we calculated that  $\overline{A}$ ,  $\overline{B}$  is the complement of (A + B)

Thus,

$$(\overline{A} + \overline{B}) = (\overline{A} \cdot \overline{B})$$

And

$$(\overline{A.B}) = (\overline{A} + \overline{B})$$

by duality.

Q 18. Prove the following identities using Boolean algebra :

(a)

$$(A + B)(A + \overline{AB}) + \overline{A}(B + \overline{C}) + \overline{AB} + ABC = C(A + B) + \overline{A}(B + \overline{C})$$

(b)

$$\overline{A(A.B)}.\overline{B(A.B)} = A \oplus B.$$

(c)

$$\overline{AB} + \overline{A} + AB = 0$$

.

(PTU, May 2008)

Ans.

$$(a)(A+B)(A+\overline{AB})C+\overline{A}(B+\overline{C})+\overline{A}B+ABC$$

$$=\left(A+B\right)\,\left(A+\overline{A}+\overline{B}\right)\,C+\overline{A}\left(B+\overline{C}\right)+B\left(\overline{A}+AC\right)$$

$$= (A + B) (1 + \overline{B})C + \overline{A}(B + \overline{C}) + B(\overline{A} + C)$$

$$(:\overline{A} + AC = \overline{A} + C)$$

$$= (A + B) C + \overline{A} (B + \overline{C}) + \overline{A}B + BC$$

$$(:BC+BC=BC, \overline{A}B+\overline{A}B=\overline{A}B)$$

$$= C (A + B) + \overline{A} (B + \overline{C}) = R.H.S$$

Hence proved.

(b)

$$\overline{A(A.B)}.B(\overline{A.B)}$$

$$= \left[\overline{A\left(\overline{A.B}\right)}\right] + \left[\overline{B\left(\overline{A.B}\right)}\right]$$

$$= \left[ A\left( \overline{A.B} \right) \right] + \left[ B\left( \overline{A.B} \right) \right]$$

$$=$$

$(A.B)$   $(A + B)$

$$= (\overline{A} + \overline{B}) (A + B)$$

$$=\overline{A}A+\overline{A}B+\overline{B}A+\overline{B}B$$

(: A = A)

Logic Circuit :

Q 21. Simplify the following boolean functions using K-maps.

(a) F (A, B, C) =  $\Sigma$  (0, 2, 3, 4, 6)

(b)  $F(A, B, C, D) = \Sigma (1, 3, 5, 7, 9, 15), d(A, B, C, D) = \Sigma (4, 6, 12, 13)$

(PTU, Dec. 2007)

Ans. (a) F (A, B, C) = Σm (0, 2, 3, 4, 6)

| A | B | · BC | ВĈ  | BC  |  |

|---|---|------|-----|-----|--|

| Ā | 1 | 0    | 13  | 1)2 |  |

| A | 1 | 0 5  | 0 7 | 1 6 |  |

$$\therefore$$

F(A, B, C) =  $\overline{A}B + \overline{C}$ .

**(b)** F (A, B, C, D) =  $\Sigma$ m (1, 3, 5, 7, 9, 15) +  $\Sigma$ d (4, 6, 12, 13)

| CO       |     |      |

|----------|-----|------|

| AB CO CO | CD  | CD   |

| AB 0 0 1 | 1   | 0    |

| AB d     | 1)  | d 2  |

| AB d d   | . 2 | - 6  |

| AB 0 12  | 15  | 0 14 |

| 8 / 8    | 0   | 0 10 |

put

$$d_{13} = 1$$

and  $d_4 = d_{12} = d_6 = 0$

$$F(A, B, C, D) = \overline{C}D + \overline{A}D + BD$$

.

$(: \overline{C} + C = 1)$

Boolean Algebra

Implementation using NAND gates only:

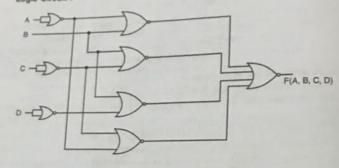

Q 20. Minimise the logic function

$F(A, B, C, D) = \pi M(1, 2, 3, 8, 9,10, 11, 14). d(7, 15)$

Use Karnaugh map. Draw the logic circuit for the simplified function using NOR (PTU, May 2008)

Ans. F (A, B, C, D) =  $\pi$ M (1, 2, 3, 8, 9,10, 11, 14). d (7, 15)

| AB CD | C+D  | C+D  | Ĉ+Ō  | Ē+D │ |                |

|-------|------|------|------|-------|----------------|

| A+B   | 1 0  | 0    | 0    | 0     |                |

| A+B   | 1 4  | 1 5  | d    | 1     | 6              |

| Ā+Ē   | 1 12 | 1 13 | d 18 | 0     | G <sub>4</sub> |

| Ā+B   | 0    | 0 9  | 0    | 0     |                |

| G     | , Go | 1    | П    |       | G <sub>3</sub> |

$$(B) = \overline{A} + B$$

$$\therefore \quad F(A, B, C, D) = G_1, G_2, G_3, G_4$$

Where,

$$G_1 = \overline{A} + B$$

$$G_2 = B + \overline{D}$$

$$G_3 = B + \overline{C}$$

$$G_4 = \overline{A} + \overline{C}$$

(: d = 0 for 15th cell in k-map for minimization)

$$\therefore \quad F(A, B, C,D) = (\overline{A} + B) (B + \overline{D}) (B + \overline{C}) (\overline{A} + \overline{C})$$

For NOR gates implementation, we have

$$\overline{F}(A, B, C, D) = \overline{(\overline{A} + B)(B + \overline{D})(B + \overline{C})(\overline{A} + \overline{C})}$$

$$\overline{F}(A, B, C, D) = \overline{(\overline{A} + B)(B + \overline{D})(B + \overline{C})(\overline{A} + \overline{C})}$$

$$F(A, B, C, D) = \overline{(\overline{A} + B) + (B + \overline{D}) + (\overline{B} + \overline{C})}$$

$$= \overline{AC} + \overline{ACD} + BC$$

$$= \overline{AC} (1+D) + BC$$

$$= \overline{AC} + BC$$

$$= C(\overline{A} + B).$$

Q 29. Using Boolean Algebra show that

$(A+B)(\overline{A}+C)(B+C)=AC+B\overline{A}$ .

(PTU, May 2010)

Ans.

$$(A+B)(\overline{A}+C)(B+C)$$

$$= (A\overline{A} + AC + B\overline{A} + BC) (B + C)$$

$$= (AC + \overline{A}B + BC) (B + C)$$

$$= ABC + AC \cdot C + \overline{A}B \cdot B + \overline{A}BC + BC \cdot B + BC \cdot C$$

$$= ABC + AC + \overline{A}B + \overline{A}BC + BC + BC$$

$$= AC \cdot (B + 1) + \overline{A}B \cdot (1 + C) + BC$$

$$= AC + \overline{A}B + BC$$

$$= AC + \overline{A}B + BC$$

$$= AC + \overline{A}B + BC (\overline{A} + A)$$

$$= AC + \overline{A}B + \overline{A}BC + ABC = \overline{A}BC \cdot (1 + C) + AC \cdot (1 + B)$$

$$= \overline{A}B + AC$$

$$(\because 1 + C = 1 + B = 1)$$

$\therefore (A+B)(\overline{A}+C)(B+C) = AC+B\overline{A}.$

Q 30. Minimize the following expressions using K-map

(a)

$$Y = (A + B)(A + \overline{B})(A + \overline{C})$$

(PTU, May 2011)

Ans. (a)

$$Y = (A + B)(A + \overline{B})(A + \overline{C})$$

K-map:

| CI  | 0   |       |    |    |

|-----|-----|-------|----|----|

| AB  | 00  | 01    | 11 | 10 |

| A 4 | 10  | 0     | 0  | 0  |

| 01  | 0   | 0     | 0  | 0  |

| 11  | 1   | 1     | 1  | -  |

| 10  | 1   | 1     | 1  | -  |

|     | 100 | Y = / | A  | 1  |

K-map:

$$= AB (C + \overline{C}) + (A + \overline{A}) BC + \overline{A} (B + \overline{B}) (C + \overline{C})$$

$$= ABC + AB\overline{C} + ABC + \overline{A}BC + (\overline{A}B + \overline{A}\overline{B}) (C + \overline{C})$$

$f = ABC + AB\overline{C} + \overline{A}BC + \overline{A}BC + \overline{A}B\overline{C} + \overline{A}\overline{B}C + \overline{A}\overline{B}C$

The above form is the standard SOP form.

## Q 27. Construct the truth table for $Z = xy + \overline{x}\overline{y}$

Ans.  $Z = xy + \overline{x}\overline{y} = x \odot y \text{ i.e., XNOR gate.}$

Its truth table is

| x | v | xv | χ̈̈ |                                 |

|---|---|----|-----|---------------------------------|

| 0 | - | ~y | ху  | $xy + \overline{x}\overline{y}$ |

| 0 | 0 | 0  | 1   | 1                               |

| 0 | 1 | 0  | 0   | 0                               |

| 1 | 0 | 0  | 0   | - 0                             |

| 1 | 1 | 1  | 0   | 1                               |

### Q 28. Minimize the following expressions

(i)

$$A + \overline{(B + \overline{C})}$$

(ii)

$$\overline{\left(A\overline{B}\left(C+\overline{D}\right)+\overline{C}\right)}$$

(PTU, May 2011)

(PTU, May 2011)

Ans. (i)

$$A + \overline{(\overline{B} + \overline{C})}$$

$$= A + \left(\overline{B}, \overline{C}\right)$$

$$= A + BC$$

(DeMorgain Theorem)

(ii)

$$\overline{\left(A\overline{B}\left(C+\overline{D}\right)+\overline{C}\right)}$$

$$= \overline{\left( \overline{A} \, \overline{\overline{B}} \, C + A \, \overline{\overline{B}} \, \overline{\overline{D}} \right)} \, . \, \overline{\overline{C}}$$

$$= \left(\overline{ABC}\right)\left(\overline{ABD}\right).C$$

$$= (\overline{A} + B + \overline{C})(\overline{A} + B + D).C$$

$$= (\overline{A} + \overline{A}B + \overline{A}D + \overline{A}B + B + BD + \overline{A}\overline{C} + B\overline{C} + \overline{C}D)C$$

$$= \overline{AC} + \overline{ABC} + \overline{ACD} + BC + BCD + 0 + 0 + 0$$

$$= \overline{AC} (1+B) + \overline{ACD} + BC (1+D)$$

(PTU, May 2006)

(PTU, Dec. 2006)

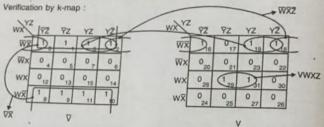

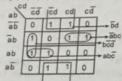

Q 24. Simplify the Boolean function :  $F\left(W,\,X,\,Y,\,Z\right)=\Sigma m\;(0,\,1,\,2,\,4,\,5,\,6,\,8,\,9,\,12,\,13,\,14\right)$

Ans.

|    | Z VZ | ΨZ  | YZ   | ΥZ   |

|----|------|-----|------|------|

| WX | 1    | 1   | 0 3  | 1 2  |

| ₩x | 7    | 1   | 0,   | 1    |

| wx | 1    | 1   | 0,   | 1    |

| wx | 1 0  | 1 9 | 0,11 | 0,10 |

$\therefore F(W, X, Y, Z) = \overline{Y} + \overline{W}\overline{Z} + X\overline{Z}$

Q 25. Simplify the following Boolean function in :

(a) Sum of products (b) Product of sums  $F(A, B, C, D) = \Sigma(0, 1, 2, 5, 8, 9, 10).$

Ans.  $F(A, B, C, D) = \Sigma(0, 1, 2, 5, 8, 9, 10)$

(a) Sum of products from i.e. min terms

$F(A, B, C, D) = \Sigma m (0, 1, 2, 5, 8, 9, 10)$

| AB CI | D<br>RD | ĒФ  | CD   | сĒ   |

|-------|---------|-----|------|------|

| ĀB    | 10      | 0,  | 0 3  | 1/2  |

| ĀB    | 0 4     | 1   | 0 7  | 0 6  |

| AB    | 0,12    | 0,3 | 0,15 | 0,14 |

| AB    | 1       | 1)0 | 0,1  | 110  |

|       | V       | 18  | -    | 1    |

$F = \overline{BC} + \overline{BD} + \overline{ACD}$

### (b) Product of sums i.e. min terms

$F(A, B, C, D) = \Sigma M \text{ or } \pi (0, 1, 5, 8, 9, 10)$

| C   | D    |     |     |     |   |

|-----|------|-----|-----|-----|---|

| AB  | 100  | 01  | 11  | 10  |   |

| ,   | 6    | 0,  | 13  | 0   | 1 |

| -   | 1 4  | 0   | 1,  | 1 6 |   |

|     | 1,12 | 1,3 | 1,5 | 1,4 |   |

| 10/ | 0    | 0   | 1,1 | (P) |   |

|     | 1    |     |     | 7   |   |

$$F = (B + C) (B + D) (A + C + \overline{D})$$

Q 26. Find SOP form of  $f = AB + BC + \overline{A}$ .

$$f = AB + BC + \overline{A}$$

(PTU, May 2010)

Boolean A

The

Q

An

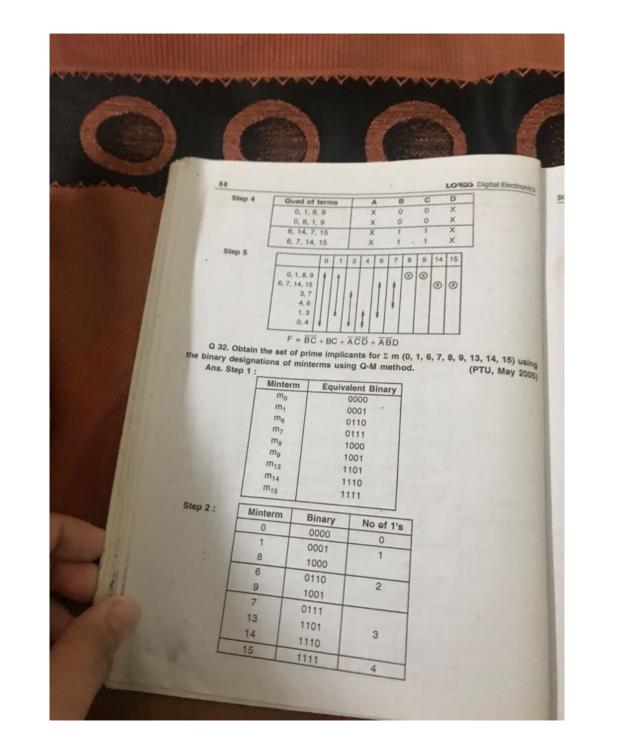

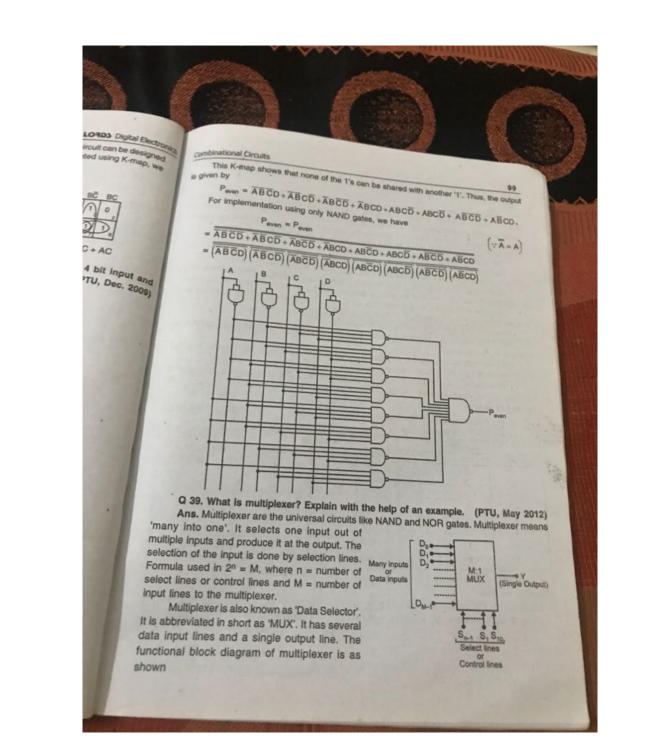

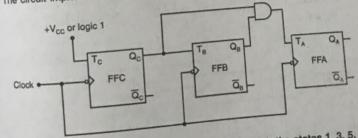

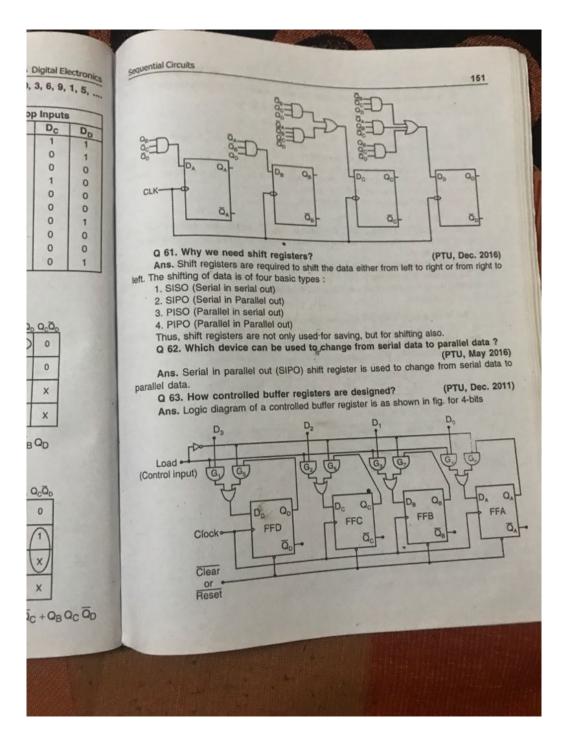

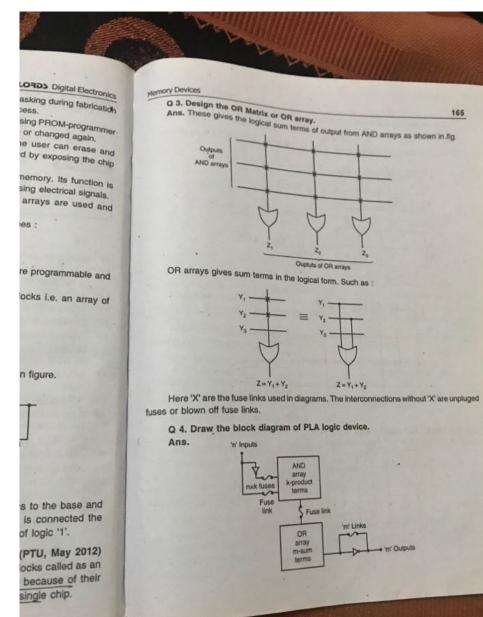

STATE OF THE PARTY. THE THEORY IS NOT THE OWNER, THE PARTY AND ADDRESS. per livery designations of movement saling 2 - 3 regime. (2010), 3mc, 3105) Shington. Bounty 170(0) ATTE. 300001 BECOME ! 100gg 980771 /ITEN (0)(00) (Tipe 20150 The . GD2551 The 10000 平二本 ITEm. 16801 Wine. 10000 The same 15551 I-D Witterna Siego (2) No. of The -30 THE . 30000 (000001) 1000 100 OTHER. B-3 (Tibe TODAY 海田 THE . The same E-T 馬 (000) dinn: -THE R. 100.00 1 0 1 8 Simp B (Paints of terms X 8 (周,司) S255 0 0 X 0 图.相 0 0 1 × (图图) 0 1 出海 0 10 3 X 出題 0 1 1 3 (4,5) 0 0 X 10. 田,田 13. 瓜刀 X 0 鱼两 5.5 X 医.14 原,梅 X (54.1百)

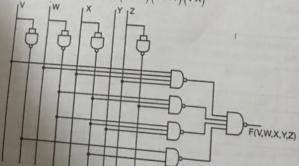

The rest 1, 8, 9, 10, 11 are to be covered from remaining prime implicants. Thus, the minimized expression is

$F(V, W, X, Y, Z) = VWXZ + \overline{W}\overline{X}\overline{Z} + \overline{W}\overline{X}Y + \overline{V}\overline{X}$

$\therefore \ \ \mathsf{F} \ (\mathsf{V}, \, \mathsf{W}, \, \mathsf{X}, \, \mathsf{Y}, \, \mathsf{Z}) = \mathsf{VWXZ} + \ \overline{\mathsf{W}} \, \overline{\mathsf{X}} \, \overline{\mathsf{Z}} + \overline{\mathsf{W}} \, \overline{\mathsf{X}} \, \mathsf{Y} + \overline{\mathsf{V}} \, \overline{\mathsf{X}}$

Hence, verified.

Implementation using NAND gates only

$$\overline{F} = \overline{VWXZ + \overline{W}\overline{X}\overline{Z} + \overline{WX}Y + \overline{V}\overline{X}}$$

$$= \overline{(VWXZ)} \, \overline{(\overline{W}\overline{X}\overline{Z})} \, \overline{(\overline{W}\overline{X}Y)} \, \overline{(\overline{V}\overline{X})}$$

Q 35. Convert the following logic functions in a product of maxterms form. F(A, B, C') = (A' + B) (B' + C') (PTU, Dec. 2016) F(A, B, C) = (A' + B) (B' + C')

F (A, B, C) =

$$(A' + B) (B' + C')$$

=  $(A' + B + C) (A' + B + C') (A + B' + C') (A' + B' + C')$

Boolean Algebra

Q 36. Obt using the bina Ans.

> Minte m m m m m m

Minte m Digital Electronics verify the result using

, 31)

soolean Algebra

Table showing minterm quads i.e. groups of four is given below

| Minterm<br>Quads | v | W | inary | Equiva | lent Z             | Number of 1's                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 1        |

|------------------|---|---|-------|--------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 0, 1, 2, 3       | 0 | 0 | 0     | X      | XI                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1        |

| 0, 2, 1, 3       | 0 | 0 | 0     | X      | x VW               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ⇒ VWX    |